PRESS RELEASE

2025年4月22日

富士通株式会社

国立研究開発法人理化学研究所

世界最大級の256量子ビットの超伝導量子コンピュータを開発

ハイブリッド量子コンピューティングプラットフォームの量子ビット数を4倍に増強し、計算能力を拡大

富士通株式会社(注1)(以下、富士通)と国立研究開発法人理化学研究所(注2)(以下、理研)は、2021年に共同で設立した「理研RQC-富士通連携センター」(以下、連携センター)において、2023年10月に公開した国産二号機となる64量子ビット超伝導量子コンピュータの開発技術をベースに、新たに開発した高密度実装技術により、世界最大級(注3)となる256量子ビットの超伝導量子コンピュータを実現しました。両者は、本256量子ビット超伝導量子コンピュータを、ハイブリッド量子コンピューティングプラットフォーム「Fujitsu Hybrid Quantum Computing Platform」(以下、ハイブリッドプラットフォーム)を通じて、2025年度第一四半期中に企業や研究機関に向けて提供を開始します。

ハイブリッドプラットフォームの計算能力が64量子ビットから256量子ビットへと4倍に拡大したことにより、利用者は、従来よりも大きな分子の解析や、多くの量子ビットを使用したエラー訂正アルゴリズムの実装と実証実験が可能となります。また今後、ハイブリッドプラットフォームにおいては、量子コンピュータと現行コンピュータが連携して、量子と現行コンピュータのハイブリッドアルゴリズムを効率的に実行する機能も実装し、ユーザビリティを向上させていきます。

富士通と理研は今後、1,000量子ビット超級の超伝導量子コンピュータを実現するために、量子ビットチップの設計や製造技術の高度化、また、高精度な量子ゲートを実現する技術開発にも取り組んでいきます。富士通はハイブリッドプラットフォームを介して、金融や創薬をはじめとする様々な分野の共同研究を行う国内外の企業や研究機関などに、より大規模な量子コンピュータを提供し、量子アプリケーションの研究開発を推進するとともに、ハードウェアとソフトウェアの両面から量子コンピュータの実用化を加速していきます。

背景

複雑かつ難解な社会課題に直面する現代社会においては、従来のコンピュータでは処理しきれない計算量の多い問題が増加しており、その解決策として量子コンピュータの実用化が強く期待されています。現在、様々な方式の量子コンピュータが開発されていますが、NISQ(ノイズが多い中規模量子デバイス)と呼ばれる現行の量子コンピュータでは、ノイズの影響を完全に排除できず、また大規模計算になるほど正確な結果が得られず、実用的な問題を解くには多くの課題が残されています。一方、完全に正確な計算が可能なFTQC(誤り訂正量子コンピュータ)の実現には、大量の量子ビットでエラーを訂正する必要があり、初期段階のFTQC(early-FTQC)で実用レベルの計算問題を解けるようになるには、少なくとも6万量子ビットが必要(注4)と予測されています。

富士通と理研は、連携センターで協力して超伝導量子コンピュータの研究開発を実施しており、量子コンピューティング分野の発展のため、現行コンピュータによる量子シミュレータと64量子ビットの量子コンピュータのハイブリッドプラットフォームを2023年10月から国内の企業や研究機関に向けて提供開始し、順次、国外へ展開しています。

新たに開発した256量子ビット超伝導量子コンピュータについて

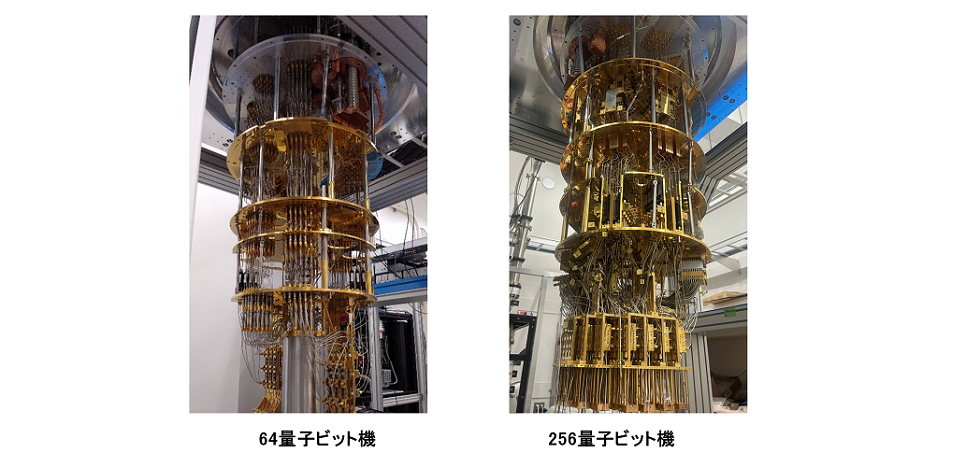

256量子ビット超伝導量子コンピュータは、理研が、文部科学省の助成(注5)を受けて、2023年3月に公開した国産初号機となる64量子ビット超伝導量子コンピュータをベースに、連携センターが2023年10月に公開した国産二号機である64量子ビット超伝導量子コンピュータを拡張して実現しました。

超伝導量子コンピュータの大規模化に向けては、量子ビットの集積化だけでなく、極低温状態を保つために希釈冷凍機内に発生する熱と冷却能力をバランスする熱設計と高密度実装が重要な課題となっています。今回、それらの技術的課題を克服し、量子コンピュータの演算機能の中心を担う量子ビットチップを、64量子ビットから256量子ビットに大幅に拡充し、計算能力の拡大を実現しました。

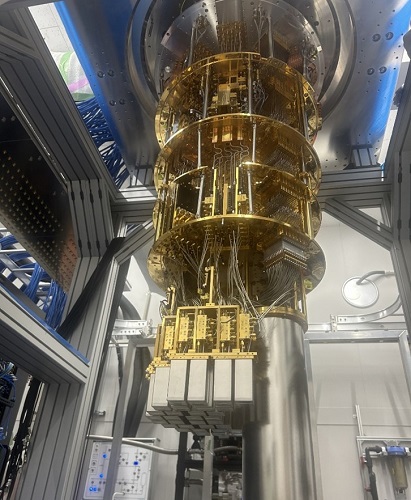

開発した256量子ビットの超伝導量子コンピュータ

開発した256量子ビットの超伝導量子コンピュータ1.3次元接続構造により量子ビットチップを容易に大規模化

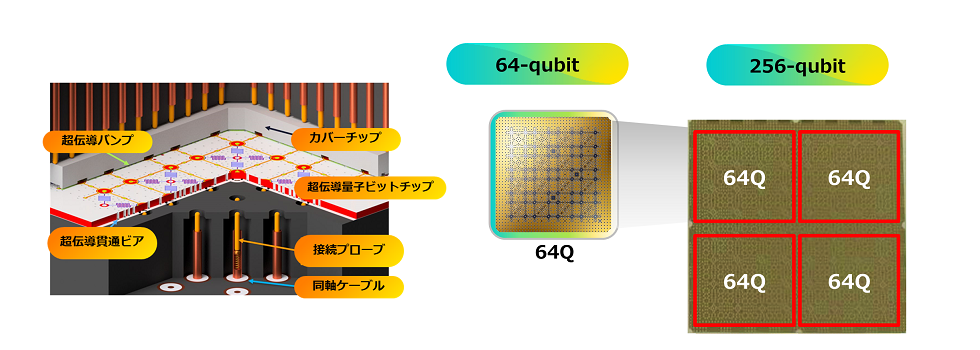

富士通と理研は、将来の超伝導量子コンピュータの大規模化に備えて、64量子ビット機の段階から3次元接続構造を採用し、量子ビットチップの拡張性を高めています。この構造は、4量子ビットから構成される単位セルを並べることで、量子ビットの設計やレイアウト変更をせずに、量子ビット数を容易に大規模化する構造です。

今回開発した256量子ビット機では、64量子ビット機で確立した単位セルの設計をベースに、3次元接続構造により量子ビットチップの拡張性が担保できることを実証しました。

3次元接続構造と256量子ビットまでの拡張性

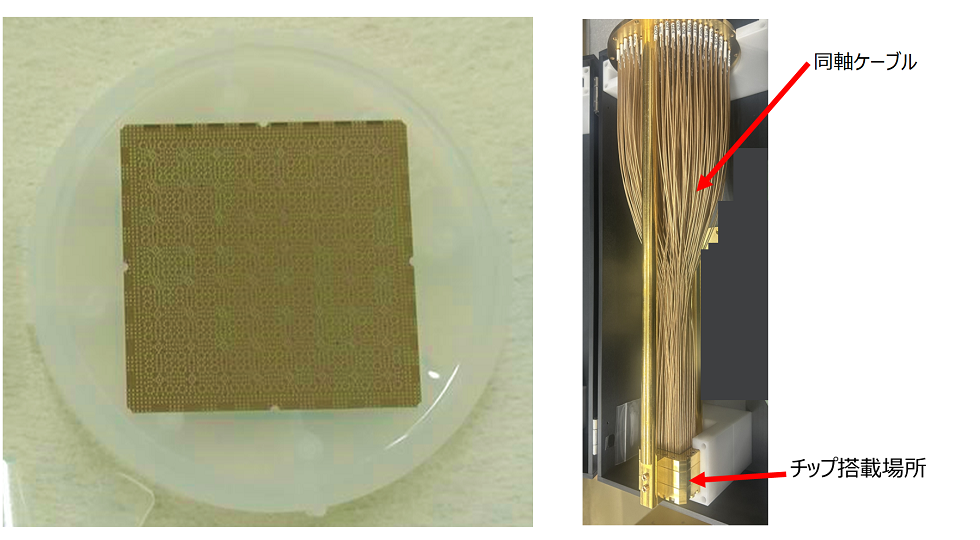

3次元接続構造と256量子ビットまでの拡張性 256量子ビットチップと3次元接続構造用サンプルパッケージ

256量子ビットチップと3次元接続構造用サンプルパッケージ2.希釈冷凍機内部の実装密度を4倍にし、64量子ビット機と同じ冷凍機を採用しながら256量子ビット機を実現

量子ビット数の大規模化に向けては、希釈冷凍機の大規模化を進めるだけでは限界があるため、希釈冷凍機内部の高密度実装を進める必要があります。希釈冷凍機は、内部を真空かつ極低温(約20ミリケルビン、摂氏-273.13度)に保持するため、使用可能な内部の体積は限定されており、同時にメンテナンス性の観点から、希釈冷凍機内部の部材占有率を抑える必要があります。また、希釈冷凍機の冷却能力と搭載される制御回路などの発熱を考慮して、冷凍機内部の熱収支のバランスを設計し、極低温を保持できるようにする必要があります。今回開発した256量子ビット機では、これら多様な要件を満たす緻密な設計を行い、冷凍機内部の熱収支をバランスさせることで、64量子ビット機と同じ希釈冷凍機を使用しながら、4倍となる実装密度を実現しました。

超伝導量子コンピュータの内部実装

超伝導量子コンピュータの内部実装今後について

富士通と理研は、2021年4月の連携センター発足当初から、超伝導量子コンピュータを1,000量子ビット級に大規模化するためのハードウェアとソフトウェア技術の開発を行ってきました。両者は、今回開発したこれらの技術も適用し、2026年の1,000量子ビットコンピュータの構築ならびに公開に向けて研究開発を進め、Fujitsu Technology Park(富士通の本店、神奈川県川崎市中原区)に建設する量子棟に設置する予定です。

また、連携センターの設置期間を当初予定の2025年3月までから2029年3月まで延長し、今後も継続して、さらなる大規模な超伝導量子コンピュータの実現を可能とする技術の研究開発に長期的に取り組みます。開発技術は、ハイブリッドプラットフォームの量子コンピュータに順次適用し、継続的に性能を向上していきます。

商標について

記載されている製品名などの固有名詞は、各社の商標または登録商標です。

注釈

-

注1富士通株式会社:

本店 神奈川県川崎市中原区、代表取締役社長 時田 隆仁 -

注2国立研究開発法人理化学研究所:

本部 埼玉県和光市、理事長 五神 真 -

注3世界最大級:

外部ユーザーに提供されている超伝導量子コンピュータとしては世界最大級(2025年4月現在、富士通調べ) -

注4少なくとも6万量子ビットが必要:

高効率位相回転ゲート式量子計算アーキテクチャにより、6万量子ビットを用いて、現行コンピュータで約5年かかる物質のエネルギー推定計算が約10時間で実行可能になる。 -

注5文部科学省の助成:

光・量子飛躍フラッグシッププログラム(Q-LEAP)「超伝導量子コンピュータの研究開発(研究代表者:中村泰信)Grant No.JPMXS0118068682」

関連リンク

- 理化学研究所と富士通、超伝導量子コンピュータの実用化に向けて連携センターを開設(2021年4月1日プレスリリース)

- 超伝導量子コンピュータを開発し、量子シミュレータと連携可能なプラットフォームを提供(2023年10月5日プレスリリース)

- 数万量子ビットの量子コンピュータでも、現行コンピュータを超える速度で実用アルゴリズムを実行する方法を確立(2024年8月28日プレスリリース)

共同記者説明会

2025年4月22日開催

本件に関するお問い合わせ

国立研究開発法人理化学研究所

富士通株式会社

-

富士通コンタクトライン(総合窓口)

0120-933-200(通話無料)受付時間: 9時~12時および13時~17時30分(土曜日・日曜日・祝日・富士通指定の休業日を除く)

-

Webでのお問い合わせ

入力フォームへ当社はセキュリティ保護の観点からSSL技術を使用しております。

プレスリリースに記載された製品の価格、仕様、サービス内容などは発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。