PRESS RELEASE

2024年2月19日

富士通株式会社

量子シミュレータの量子回路計算を200倍高速化する技術を開発

量子コンピュータの実用化に向けたアルゴリズム開発を加速

当社はこのほど、量子シミュレータ上で、量子コンピュータの初期の使用方法として提案されている量子・古典ハイブリッドアルゴリズムを、従来のシミュレーション所要時間と比較して200倍高速に実行できる技術を開発しました。

従来の量子・古典ハイブリッドアルゴリズムを活用した量子回路計算においては、解きたい問題の規模に応じて量子回路計算の回数が増大してしまい、特に材料や創薬分野のシミュレーションのように多くの量子ビットを必要とする大規模な問題では数百日も要しており課題となっていました。

今回開発した技術は、繰り返し実行される膨大な量子回路計算を複数グループに分散し同時処理を可能にしました。さらに当社が開発した世界最大級の量子シミュレータを使うことで、規模が大きな問題では、精度の劣化を抑えつつ問題を単純化できる手法を導出しました。これらを合わせて、従来方式では200日かかると想定されていた量子シミュレータでの計算を、わずか1日で実行可能にする技術を世界で初めて開発しました。これにより、これまで難しかった大規模量子計算のシミュレーションを現実的な時間で完了できるようになり、量子・古典ハイブリッドアルゴリズムでより大きな分子を計算した場合の挙動をシミュレーションし、アルゴリズム開発につなげることが可能になりました。

当社は今後、本技術を当社のハイブリット量子コンピューティングプラットフォーム「Fujitsu Hybrid Quantum Computing Platform」に搭載し、金融や創薬をはじめとする様々な分野での量子コンピュータの実用化検討を加速します。さらに本技術を応用して、量子シミュレータのみならず、量子コンピュータでの量子回路計算を加速できることを検証していきます。

背景

現在、誤り耐性量子コンピュータ(FTQC、注1)の開発が世界的に進んでいますが、現状の量子コンピュータはノイズの影響を除去しきれないなどの多くの課題があります。一方で、FTQCに先んじて量子コンピュータの有用性を示すため、100から1,000量子ビットの小・中規模でノイズを許容する量子コンピュータ(Noisy Intermediate-Scale Quantum Computer, NISQ)向けの実応用の検討も進められています。

代表的なNISQ向けのアルゴリズムであるVQE(注2)を応用することで、例えば、当社は量子アプリケーション開発のための量子シミュレータを開発(注3)し、量子回路計算そのものの高速化に取り組んできました。しかしVQEは、問題の規模の増大に伴い量子回路計算の繰り返し回数が増加するため、計算の実行には非常に時間がかかり、特に多くの量子ビットを要求する大規模な問題では、量子シミュレータの場合、数百日程度要すると試算されます。そのため、実用に向けた量子アルゴリズムの開発が難しく課題でした。

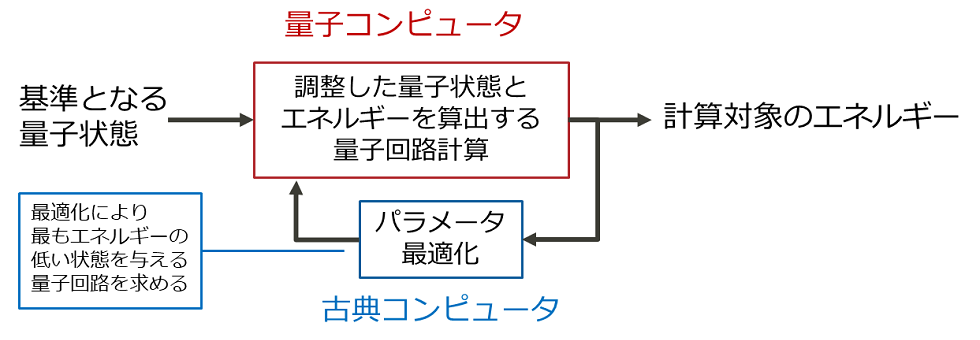

図1 VQEの全体フロー

図1 VQEの全体フロー開発した技術

当社はこの問題に対し、繰り返し実行される量子回路計算を複数同時に分散処理し、さらに精度の劣化を抑えて量子回路計算量を削減することで、200倍の高速化を実現する技術を開発しました。

量子回路の繰り返し計算を必要とする最適化処理の分散同時実行

量子・古典ハイブリッドアルゴリズムでは、量子回路計算を実行する処理と、古典コンピュータを利用して量子回路のパラメータ(注4)を最適化する処理を交互に繰り返すことで、最もエネルギーの低い状態、例えば分子の基底状態を与えるような量子回路を求めています。しかし、古典コンピュータによる量子回路のパラメータ最適化では、パラメータを微小変更した膨大な量子回路を準備し、それらの回路すべてに対して量子回路計算を逐次実行し、その結果から最適なパラメータを導出する必要があるため、特に問題規模が大きい場合膨大な計算時間が必要となります。単純に回路計算を高速化するためノード数を増やすことは通信オーバーヘッドなどの影響で限界があり、新たな技術が求められていました。

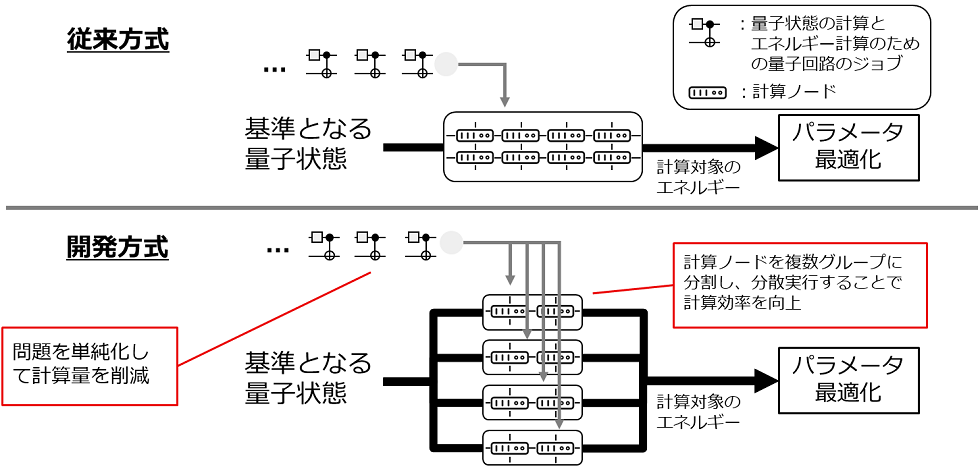

本技術では、パラメータを微小変更した量子回路それぞれが互いに影響を及ぼすことなく実行できることに着目し、量子シミュレータの計算ノードを複数のグループに分割し、RPC(注5)の技術を活用しネットワークを通して量子回路計算のジョブを投入することで、各グループが異なる量子回路を実行できる分散処理技術を開発しました。この技術を用い、パラメータの異なる複数の量子回路を同時に分散実行して最適化することを実現し、計算時間を1/70に短縮することが可能となりました。

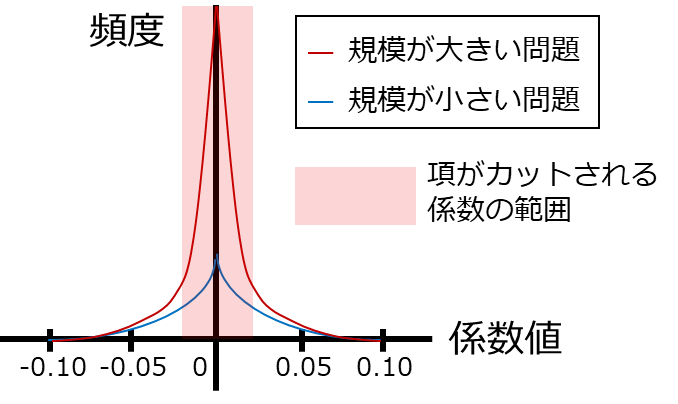

また、量子・古典ハイブリッドアルゴリズムにおける計算量は、解きたい問題における式の項数に比例し、その項数は一般的なVQEでは量子ビット数の4乗となるため、問題規模が大きくなると計算量が増大し、現実的な時間で結果を得ることが出来なくなります。当社は世界最大級(注6)となる40量子ビットの量子シミュレータの内32量子ビットを活用した規模の大きい分子のシミュレーションを通して、規模が大きくなるほど項の総数に対する係数の小さい項の割合が多くなること、かつ係数の小さい項が計算の最終結果に与える影響も微小であることを発見しました。この特性を利用し、式の項数の削減と計算精度の劣化防止を両立させることを実現し、量子回路計算時間を約80%削減できました。

図2 最適化のための量子回路計算の処理フロー

図2 最適化のための量子回路計算の処理フロー 図3 問題の規模による式の係数値の度数分布の違い

図3 問題の規模による式の係数値の度数分布の違い効果

これら2つの技術を組み合わせることで、32量子ビットの問題に対して1,024の計算ノードを8つのグループに分割して分散処理した際、従来では200日と見積もられていた32量子ビットの量子シミュレーションの実行時間を、1日で実現可能なことを世界で初めて確認することができました。これにより量子ビット数の大きい問題に対する量子アルゴリズムの開発が進み、量子コンピュータの材料・金融の分野への応用が進むことが期待されます。

富士フイルム株式会社 解析技術センター 主席研究員 奥野 幸洋氏のコメント

富士フイルムは、量子コンピュータの材料開発への応用を検討しています。その中で、NISQデバイスにおけるVQEの利用は必須な検討項目です。今回の高速化技術により、VQEアルゴリズムの原理検証が大幅に加速されることを期待しています。

東京エレクトロン株式会社 デジタルデザインセンター 部長 守屋 剛氏のコメント

弊社では、VQE活用による半導体材料に関連する分子のエネルギー計算や特定の材料の電子構造・物性予測、半導体製造プロセスにおける化学反応の最適化などを検討しています。今回の高速化により、VQEアルゴリズムの原理検証や効果検証を迅速に実施し、有用性を発見できることを期待しています。ノイズや誤りが活用を制限しているNISQデバイスにおいても、その制約を考慮しながら検討を進めていきます。

商標について

記載されている製品名などの固有名詞は、各社の商標または登録商標です。

注釈

-

注1FTQC:

Fault-Tolerant Quantum Computerの略。量子エラーを訂正しながら誤りなく量子計算が実行可能な量子コンピュータ -

注2VQE:

Variational Quantum Eigensolver(変分量子固有値ソルバー)の略。量子コンピュータによる計算と古典コンピュータによる最適化を繰り返すことで物質のエネルギーを求める技術 -

注3量子アプリケーション開発のための量子シミュレータを開発:

スーパーコンピュータ「富岳」のテクノロジーを活用し、36量子ビットの世界最速量子シミュレータの開発に成功(2022年3月30日プレスリリース) -

注4パラメータ:

基準となる量子状態を物理的に意味のある量子状態に調節するための量子回路のゲートの回転角 -

注5RPC:

Remote Procedure Callの略。あるコンピュータからネットワークなどを介して別のコンピュータ上にある処理を実行する技術 -

注6世界最大級:

汎用的な量子回路シミュレーション方式であるState Vector方式の常設専用機としては世界最大級(2024年2月現在、富士通調べ)

関連リンク

当社のSDGsへの貢献について

2015年に国連で採択された持続可能な開発目標(Sustainable Development Goals:SDGs)は、世界全体が2030年までに達成すべき共通の目標です。当社のパーパス(存在意義)である「イノベーションによって社会に信頼をもたらし、世界をより持続可能にしていくこと」は、SDGsへの貢献を約束するものです。

本件に関するお問い合わせ

-

富士通コンタクトライン(総合窓口)

0120-933-200(通話無料)受付時間: 9時~12時および13時~17時30分(土曜日・日曜日・祝日・富士通指定の休業日を除く)

-

Webでのお問い合わせ

入力フォームへ当社はセキュリティ保護の観点からSSL技術を使用しております。

プレスリリースに記載された製品の価格、仕様、サービス内容などは発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。