PRESS RELEASE (事例)

2020年9月23日

富士通株式会社

キヤノン様の新スーパーコンピュータシステムを受注

スーパーコンピュータ「富岳」の技術を活用した商用スーパーコンピュータでものづくりにおける「試作レス」開発に貢献

当社は、キヤノン株式会社(本社:東京都大田区、代表取締役会長兼社長 CEO:御手洗冨士夫、以下、キヤノン)様の新スーパーコンピュータシステムを受注しました。

本システムは、国立研究開発法人 理化学研究所(以下 理化学研究所、注1)様と当社が共同開発したスーパーコンピュータ「富岳」の技術を活用した「FUJITSU Supercomputer PRIMEHPC FX1000(プライムエイチピーシーエフエックスセン、以下 PRIMEHPC FX1000、注2)」で構成され、理論演算性能は648.8テラフロップス(以下 TFLOPS、注3)を実現予定です。

これにより、キヤノン様の製品開発プロセスにおける解析領域のさらなる高度化および多様化を実現し、製品開発における「試作レス」の取り組み(注4)に貢献します。

本システムは2021年前半から稼働予定です。

背景

キヤノン様は、複写機をはじめとする各種プリンター、カメラ、半導体露光装置などの製品開発において、3DCADデータを用いた解析シミュレーションによって製品の機能性や生産性など多面的な検証を行う「試作レス」の取り組みを推進されており、これまで当社のスーパーコンピュータ「FUJITSU Supercomputer PRIMEHPC FX10(エフエックステン、以下 PRIMEHPC FX10)」および「FUJITSU Supercomputer PRIMEHPC FX100(エフエックスヒャク、以下PRIMEHPC FX100)」を活用されてきました。

このたび、さらに大規模かつ高度な解析を行うため、高性能、高信頼、省電力を兼ね備えた当社の「PRIMEHPC FX1000」が採用されました。

新システムの概要

今回当社が構築するスーパーコンピュータシステムは、192ノードの「PRIMEHPC FX1000」で構成され、理論演算性能は648.8TFLOPSを有する見込みです。また、「FUJITSU Server PRIMERGY」や「FUJITSU Storage ETERNUS」を周辺機器として導入します。これにより、キヤノン様の製品開発における製品の落下時における破損・変形などを検証する衝突解析試験において、これまで処理することが困難であった1億要素(注5)以上の大規模な解析やシミュレーションなどが可能になります。また、従来はスーパーコンピュータを採用していなかった気流解析や電磁波解析などでも活用が可能となり、キヤノン様が取り組む「試作レス」による製品開発を強力に支援します。

当社は、「PRIMEHPC FX1000」をはじめとするテクニカルコンピューティング・ソリューションの提供を通じ、お客様の製品開発期間の短縮やコスト削減、製品の性能・品質・機能の向上に貢献していきます。

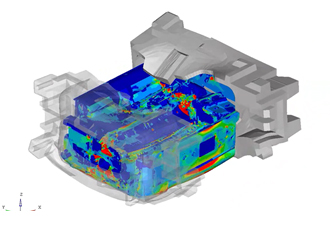

落下衝撃シミュレーションのイメージ

(インクジェットプリンターの梱包落下)

※現行システムのもの

※キヤノン様公開サイトより抜粋

今回導入する「PRIMEHPC FX1000」

※1ラック(384ノード)のイメージ

新システムの主な構成

| メインシステム | 主な構成製品 | FUJITSU Supercomputer PRIMEHPC FX1000 |

| ラック数 | 1(ハーフラック) | |

| 計算ノード数(CPUコア数) | 192(9,216) | |

| 理論演算性能 | 648.8TFLOPS | |

| 総主記憶容量 | 6テラバイト | |

| ストレージサブシステム | 総実効容量 | 1.5ペタバイト |

| 周辺サーバ・ストレージ | 主な構成製品 | FUJITSU Server PRIMERGY RX2530 M5/RX2540 M5 FUJITSU Storage ETERNUS DX60 S5/AF250 S3 |

商標について

記載されている製品名などの固有名詞は、各社の商標または登録商標です。

以上

注釈

- 注1 国立研究開発法人 理化学研究所:

- 所在地:埼玉県和光市、理事長:松本 紘

- 注2 FUJITSU Supercomputer PRIMEHPC FX1000:

- Arm®v8-A命令セットアーキテクチャーをスーパーコンピュータ向けに拡張した「SVE(Scalable Vector Extension)」を採用したCPU「A64FX」を搭載。高い電力あたり性能とともに、高性能積層メモリであるHBM2の高いメモリバンド幅による高い計算効率を実現。

- 注3 テラフロップス:

- TFLOPS(Tera Floating-point Operations Per Secondの略語表記)。Teraは1兆(10の12乗)のことで、毎秒1兆回の浮動小数点演算ができることを表す。

- 注4 「試作レス」の取組み:

- キヤノン様ではシミュレーション技術を基軸とした試作仮想化技術により無駄な製品試作をなくし、必要な試作のみ行う全社活動を推進している。

- 注5 要素:

- 解析技術分野において、コンピュータシミュレーションで現象を取り扱うために、構造物を単純形状の集合体として考える際の構成単位。小さな要素を多数用いる事で、より高精度に現象を再現可能。

関連リンク

- キヤノン株式会社 ホームページ

- CANON TECHNOLOGY:生産技術(キヤノン公開ページ)

- スーパーコンピュータ「FUJITSU Supercomputer PRIMEHPC」シリーズ紹介ページ(富士通公開ページ)

本件に関するお問い合わせ

富士通コンタクトライン(総合窓口)

![]() 0120-933-200

0120-933-200

受付時間: 9時~17時30分(土曜日・日曜日・祝日・富士通指定の休業日を除く)

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。