PRESS RELEASE (技術)

2017年12月11日

株式会社富士通研究所

FPGAアクセラレータを活用したWAN高速化技術を開発

10Gbps回線で業界最高の最大40Gbpsの実効転送速度を実現

株式会社富士通研究所(注1)(以下、富士通研究所)は、FPGAを搭載したサーバを活用することにより、クラウド間の大量データ転送において最大毎秒40ギガビット(以下、Gbps)の転送速度を実現するWAN高速化技術を開発しました。

クラウド間のWAN(Wide Area Network)回線は1Gbpsから10Gbpsへの移行が進みつつありますが、近年のIoT、AIといったデジタル技術の発展に伴い、大量のデータがクラウド上に集まり、より高速なデータ転送が求められています。従来、転送データの圧縮や重複除去などのWAN高速化技術によって、WAN回線における実効転送速度の向上を実現していましたが、WAN回線が10Gbpsになると処理すべきデータ量が非常に多く、十分に実効転送速度を向上できませんでした。

今回、WAN高速化技術における特徴量計算や圧縮処理などの各処理に特化した専用演算器を、サーバに搭載されたFPGA(注2)上に配置するとともに、予測した各処理の完了タイミングに合わせてデータを演算器に供給することで高並列動作を可能とし、10Gbps以上でも実時間動作が可能なWAN高速化技術を開発しました。本技術をFPGA搭載サーバに実装し、サーバ間を10Gbps回線で接続した実験環境において、業界最高性能となる最大40Gbpsの実効転送速度を確認しました。本技術により、クラウド間でのデータ共有やバックアップなどのデータ転送を高速に行うことが可能となり、様々な企業・拠点間で大量のデータを共有し活用する次世代のクラウドサービスを実現します。

富士通研究所は、本技術をクラウド環境で利用可能なFPGA搭載サーバ上のアプリケーションに実装し、実環境での評価を進め、2018年度中の実用化を目指します。

本技術の詳細は、12月11日(月曜日)から13日(水曜日)までオーストラリア メルボルンで開催予定の国際会議「FPT 2017 (The 2017 International Conference on Field-Programmable Technology)」にて発表します。

開発の背景

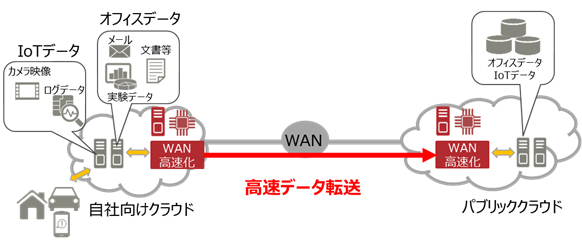

近年、クラウドの進展に伴い、企業内のサーバで管理していたデータ(社内文書、設計データ、電子メールなど)をクラウド上に移行することで、データやサーバの管理・保守を効率化する動きが進んでいます。また、IoT、AIなどのデジタル技術の活用も広がりを見せており、工場や現場のカメラ映像、機器のログデータなど大量のデータを分析、活用することによる業務やビジネスの革新への期待が高まっています。これにともない、クラウド間のWAN回線を流れるデータ量が爆発的に増加するため、クラウド間で大量のデータを高速に転送可能な次世代のWAN高速化技術が求められています。

図1 クラウド環境におけるWAN高速化技術の利用例

課題

WAN高速化技術では、転送されるデータの圧縮や重複除去によりデータ量を削減することで実効的な転送速度を向上します。10Gbpsのネットワーク回線で、さらなる高速データ転送を行う場合、処理すべきデータ量が多く、サーバ内での圧縮・重複除去の処理速度がボトルネックとなっていました。したがって、実時間動作のためには、より高速動作可能なCPU、もしくは、より処理速度の速いWAN高速化技術が求められていました。

開発した技術

今回、サーバに搭載したFPGAをアクセラレータとして活用し、クラウド上での利用が可能で10Gbps以上でも実時間動作が可能なWAN高速化技術を開発しました。本技術では、WAN高速化処理における圧縮や重複除去のうち、負荷が重くCPUでの処理速度向上が難しい一部の処理をFPGAで実行し、CPUとFPGAアクセラレータを効率よく連携させることにより、WAN高速化技術の効率的な動作を実現しました。開発した技術の特徴は以下の通りです。

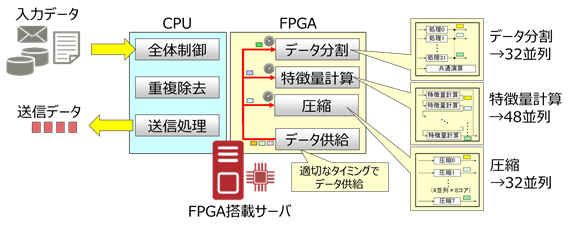

- 高並列専用演算器によるFPGA並列化技術

データ分割、特徴量計算、可逆圧縮処理に特化した専用演算器をFPGAに高並列に実装するとともに、各演算の完了予測に基づいた適切なタイミングでのデータ供給により演算器の高並列動作を可能とすることで、データの圧縮・重複除去処理に要する処理時間を大幅に削減できるFPGA並列化技術を開発しました。

図2 FPGA搭載サーバを活用したWAN高速化処理の実装

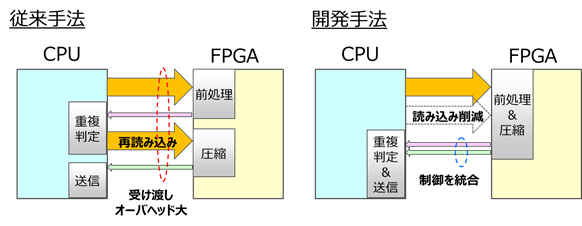

拡大イメージ - CPU-FPGA間の処理フロー最適化技術

従来は、重複判定結果に基づいて可逆圧縮処理を行うかどうかを決定するため、FPGA側で実行される重複判定の前と後の処理で2度データを読む必要があり、オーバーヘッドが大きく十分な性能が出ませんでした。今回、FPGAへの処理の切り替えを固定化し、FPGA側で重複判定前処理および圧縮処理を行っておき、CPU側で重複判定結果に基づいて圧縮処理結果の反映を制御する処理手順とすることで、CPU-FPGA間での入力データの再ロードおよび制御のやりとりによるオーバーヘッドを低減しました。これにより、CPU-FPGA間のデータや制御の受け渡しによる待ち時間を低減し、CPUとFPGAアクセラレータの効率よい連携動作を実現しました。

図3 CPU-FPGA間のオーバーヘッド低減手法の概要

効果

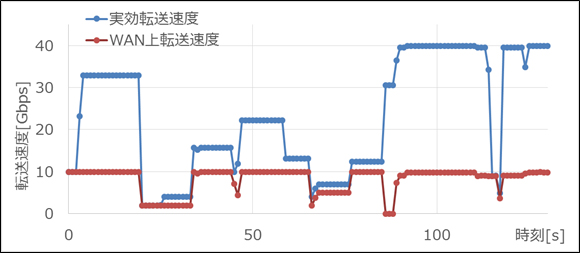

FPGAを搭載したサーバに今回開発した技術を適用し、CPUのみの処理に対して約30倍の高速化を確認しました。サーバ間を10Gbps回線で接続した実験環境において大量データの転送速度を評価し、ドキュメントや画像データなどの定期的なバックアップを模擬した実験において、業界最高となる最大40Gbpsの転送速度を確認しました。これにより、WAN回線上のデータ転送効率が大幅に向上し、クラウドでのデータ共有やバックアップなどのデータ転送を高速に行うことが可能となり、様々な企業・拠点間で大量のデータを共有し活用する次世代のクラウドサービスを実現できます。

図4 実験データでの評価結果例

今後

富士通研究所は、本技術をクラウド環境で利用可能な仮想アプライアンスに搭載し、実環境での評価を進めます。本技術を搭載した製品を、2018年度中に富士通株式会社から新規提供することを目指します。

商標について

記載されている製品名などの固有名詞は、各社の商標または登録商標です。

以上

注釈

- 注1 株式会社富士通研究所:

- 本社 神奈川県川崎市、代表取締役社長 佐々木繁。

- 注2 FPGA:

- Field Programmable Gate Arrayの略。製造後に回路構成をプログラム可能な汎用デバイス。

本件に関するお問い合わせ

株式会社富士通研究所

コンピュータシステム研究所

![]() 044-874-2105(直通)

044-874-2105(直通)

![]() wanopt_pr@ml.labs.fujitsu.com

wanopt_pr@ml.labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。