PRESS RELEASE (技術)

2017年2月6日

University of Toronto

株式会社富士通研究所

世界最小電力、光モジュールのリファレンスレス受信回路を開発

光モジュールを省電力化・小型化し、データセンターの処理能力向上に貢献

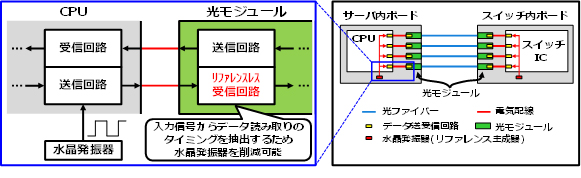

University of Toronto (注1)(トロント大学)と、株式会社富士通研究所(注2)(以下、富士通研究所)は共同で、データセンター内のサーバとスイッチ間通信で用いられるイーサネット向け光モジュールにおいて、従来の55%の電力で動作する世界最小電力のリファレンスレス受信回路(注3)を開発しました。

ビッグデータ解析やクラウドサービスの普及に伴い、サーバやスイッチ間で高いデータ転送能力を実現するため、光モジュールの高速化・高密度化が求められており、そのためには小型化と省電力化が必要とされています。

光モジュールを高速化して小型化するために、基準となるタイミングを発生させる水晶発振器が不要なリファレンスレス受信回路技術が開発されていますが、従来のリファレンスレス受信回路では、入力データを読み取るタイミング周期のズレを検出する回路の消費電力が大きく、それに伴い発生する熱の問題から高密度化が困難という課題がありました。

従来、データ読み取り周期のズレを検出するために、1ビットに対して4回の異なるタイミングで信号を検出することが必要であり、この各タイミング生成回路の消費電力がモジュール全体の消費電力のうち大きな割合を占めていました。今回、入力信号の振幅情報から読み取り周期のズレを検出することで、1ビットに対して1回と、データの伝送速度と同じ周期で動作可能な新しいタイミング抽出技術を開発しました。その結果、タイミング生成回路を4分の1に削減し、光モジュール全体の消費電力を従来の約70%に削減することに成功しました。

本技術により光モジュールの省電力化が可能となり、その分高密度実装による高いトラフィック転送能力を実現し、データセンターの処理能力を向上させることができます。

本技術の詳細は、2月5日(日曜日)から米国サンフランシスコで開催されている半導体技術に関する最大級の国際会議「国際固体素子回路会議 ISSCC 2017(IEEE International Solid-State Circuits Conference 2017)」で発表します(ISSCC 発表番号6.6)。

開発の背景

ビッグデータ解析やクラウドサービスの普及に伴い、サーバや各スイッチ間に高いデータ転送能力が求められています。そのためにはサーバとスイッチ間通信で用いられる光モジュールを高速化、小型化して、高密度に実装することが求められています。

課題

光モジュールの省電力化や小型化には搭載する部品の数を減らすことが効果的です。そのため、基準となるタイミング(リファレンス)を必要としないリファレンスレス受信回路を用いることで水晶発振器を削減することが可能となります。

しかし、従来のリファレンスレス受信回路は、入力信号を観測してデータを読み取る周期を調整するための回路を高速に動作させる必要があるため消費電力が大きく、また電力消費に伴う発熱の問題から高密度実装が困難でした。

図1 リファレンスレス受信回路を利用したCPUと光モジュール間の接続構成

拡大イメージ

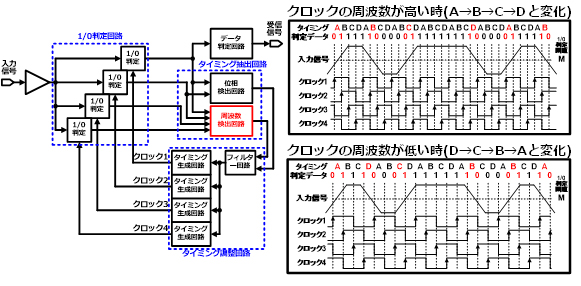

従来構成のリファレンスレス受信回路は、1ビットのデータに対し1/0判定を4回行い、それぞれの判定結果の変化を見ることでデータの読み取り周期を調整していました。

タイミング生成回路により生成されるクロック1からクロック4が、それぞれ0から1に変化するタイミングで入力信号を観測し1/0判定を行います。これによりどのクロックとどのクロックの間で判定データの1/0が変化するかを観察することができます。例えば、図2に示すようにA→B→C→Dと変化することが観察された場合はデータの読み取り周期が入力信号よりも短いということが分かります。逆にD→C→B→Aと変化することが観察された場合はデータの読み取り周期が入力信号よりも長いということが分かります。

図2 従来構成のリファレンスレス受信回路と周波数差検出

拡大イメージ

開発した技術

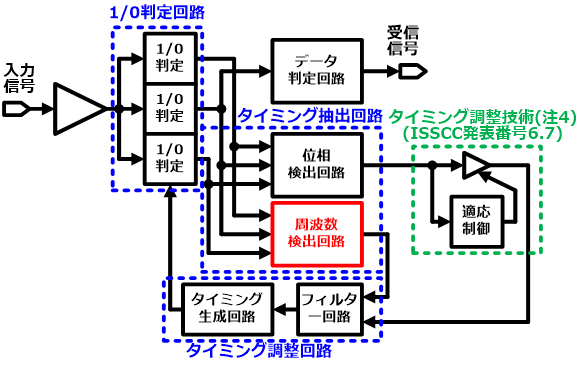

今回、入力信号の振幅情報からデータの読み取り周期のズレを検出する新しい方式により、リファレンスレス受信回路の消費電力を削減する技術を開発しました。

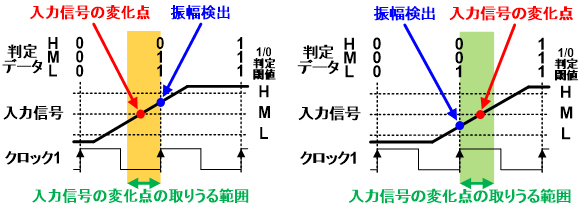

本技術では、振幅情報からデータ読み取り周期のズレを検出するために、入力信号が1か0かを判定するしきい値が高・中・低と異なる3つの判定回路を1回のタイミングで動作させて入力信号の変化の傾きを調べます。例えば、入力信号が0から1に変化する時に、クロック1のタイミングで判定した3つの結果が(0、1、1)なら入力信号の変化点はクロック1の判定タイミングよりも前(図中の黄色の範囲)で、(0、0、1)なら後(図中の緑色の範囲)と検出できます(図3)。後はそのタイミングがどのように変化していくかを調べることでタイミングのズレを検出できます。

本技術により、従来構成に比べてタイミング生成回路を4分の1に削減することが可能となります(図4)。

図3 タイミング検出方法

図4 新規構成のリファレンスレス受信回路

効果

今回開発した技術により、リファレンスレス受信回路の消費電力を従来構成に比べて55%に削減、光モジュールでは70%に削減しました。これにより光モジュールを従来に比べて高密度に実装することが可能となり、データセンターの性能向上に大きく寄与することが期待されます。

今後

富士通研究所は、開発した技術について、2019年度の実用化を目指します。

商標について

記載されている製品名などの固有名詞は、各社の商標または登録商標です。

以上

注釈

- 注1 University of Toronto:

- 所在地 Canada, Ontario州 Toronto市、学長 Meric S. Gertler。

- 注2 株式会社富士通研究所:

- 本社 神奈川県川崎市、代表取締役社長 佐々木繁。

- 注3 リファレンスレス受信回路:

- データ伝送において、受信データの1/0判定を行うタイミング情報の生成に、高精度なリファレンス信号を用いず、受信データからタイミング情報を抽出する方式の受信回路。

- 注4 タイミング調整技術:

- 温度変化やノイズの影響に対する受信回路の信頼性を向上させるタイミング調整技術(ISSCC発表番号6.7)も開発。これにより環境変動に依存せず、信頼性の高い受信回路を実現。

本件に関するお問い合わせ

株式会社富士通研究所

コンピュータシステム研究所

![]() 044-754-2692(直通)

044-754-2692(直通)

![]() hsio2017@ml.labs.fujitsu.com

hsio2017@ml.labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。