PRESS RELEASE (技術)

2012年10月29日

株式会社富士通研究所

新たな実装技術により電力の合成効率90%を達成し、

77GHz帯CMOSパワーアンプで32mWの高出力化を実現

車載レーダーや無線通信端末などに適用することで、送受信器の小型・低コスト化に貢献

株式会社富士通研究所(注1)は、車載レーダー(注2)や無線通信端末などへ適用可能な、ミリ波(注3)帯高出力増幅器(パワーアンプ)を実現する実装技術を開発しました。

ミリ波送受信用機器を小型・低コストに構築するためには、高周波無線(RF)回路をCMOS(注4)チップ上に一体集積化することが有効ですが、低電圧で動作するCMOS回路では送信部に用いられるパワーアンプの高出力化が困難であり、集積化への課題となっていました。このため、CMOSで作製したパワーアンプの高出力化を実現させる技術が望まれていました。

今回、複数個のパワーアンプから出力されるミリ波帯高周波信号をチップの外のモジュール内で合成する技術を開発しました。本技術をCMOSパワーアンプに適用してモジュールの試作を行い、77ギガヘルツ(以下、GHz)帯で32ミリワット(以下、mW)の高出力化を実現しました。これにより、高出力なパワーアンプを集積したCMOSミリ波送受信器が実現可能となり、小型・低コスト化に大きく貢献することが期待されます。

本技術の詳細は、10月28日(日曜日)からオランダで開催される国際会議「EuMC 2012(European Microwave Conference 2012)」にて発表します。

開発の背景

近年、77GHz帯車載レーダーや60GHz帯を利用した大容量無線通信端末など、ミリ波を利用したアプリケーションの普及が進みつつあります。これらのアプリケーションに用いられるRF送受信ICには、現在、高周波特性に優れた化合物半導体(注5)が適用されています。一方で、近年のCMOSテクノロジーも微細加工技術の進展により動作速度が化合物半導体並みに向上しており、RF回路を化合物半導体から低価格で大量生産可能なCMOSに置き換えるための研究が進められています。

課題

RF送受信ICをCMOSチップ上に集積化する際の課題は、送信部に使われるパワーアンプの高出力化です。微細化の進展とともにCMOSの電源電圧が低下するため、出力電力の大きなパワーアンプを実現することが難しく、化合物半導体並みの電力が得られませんでした。

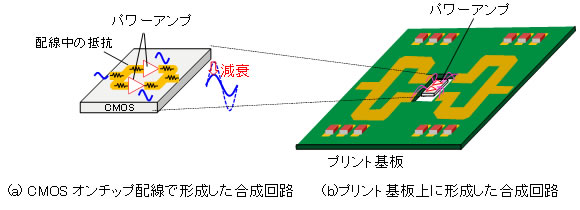

パワーアンプを高出力化させる手段として、複数個のパワーアンプを並列に配置して、その出力を合成する手法が知られています。この合成回路をCMOSオンチップ配線で形成した場合(図1(a))、配線厚が薄いため配線抵抗が大きく、パワーアンプが出力した電力に対して、出力部に到達するまでに約30%の電力が減衰し、効率が低下していました。一方で、電子機器に一般的に用いられるプリント基板上に電力合成回路を形成する場合(図1(b))、配線の微細加工が難しく、ミリ波帯の高周波信号を伝達するのが困難な上、パワーアンプを含むモジュール全体のサイズが大きくなる問題がありました。このため、小型で効率よく電力を合成する回路の実現が望まれていました。

図1 従来のパワーアンプ合成回路の形式

開発した技術

今回、パワーアンプから出力されるミリ波帯高周波信号をチップの外のモジュール内で合成する新たな実装技術(再配線技術)を開発し、ミリ波パワーアンプの高出力化を実現しました。

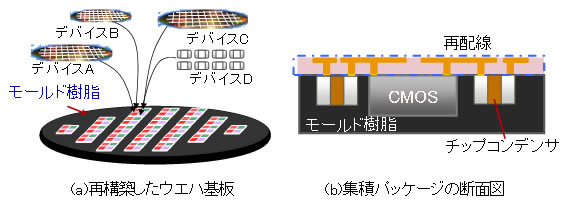

再配線技術とは、半導体部品のパッケージ形式のひとつで、チップ化された半導体素子をモールド樹脂によりウエハ状に再構築し(図2(a))、その後、配線工程を経てチップ間の端子パターンを接続するパッケージの一形態です。ウエハ状に加工されているため、微細な配線パターンを形成することが可能です。

図2(b)の断面図のように、チップコンデンサなど異なる種類のデバイスも一体集積化することができ、かつ、部品を高密度に実装することが可能です。1層の配線層から成る再配線を用いた実装技術は、これまで携帯電話などに使われる小型実装技術として発展してきましたが、ミリ波信号の伝送に適した配線構造は開発されておらず、適用例はほとんどありませんでした。

図2 再配線を適用した集積パッケージ

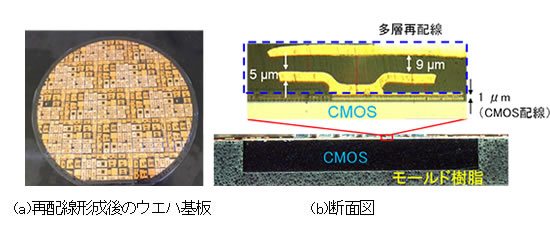

今回、ミリ波帯の高周波信号が伝達できるように、配線層を複数用いる多層配線技術を適用した電力合成器を開発しました(図3(a))。再配線で形成する配線層は、図3(b)に示すように、一般的なCMOSオンチップ配線厚に比べて5倍以上厚膜な配線層を形成することが可能です。これにより、配線における抵抗を小さくすることができ、合成器の損失を小さくできます。さらに、絶縁膜や、配線パターンの幅を最適化することにより、信号減衰が10%以下となる電力合成回路を開発しました。

図3 CMOSオンチップ配線と再配線の断面比較

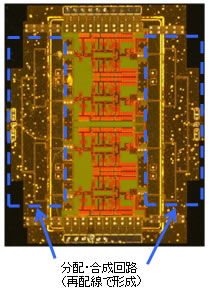

この電力合成回路をCMOSパワーアンプに適用することにより高出力なパワーアンプモジュールを開発しました(図4)。出力電力が 9mWの77GHz帯CMOSパワーアンプを4個並列に配置し、その入出力を再配線技術で形成した合成回路で接続しています。電力損失を従来の手法の約30%から10%に低減することで、電力の合成効率90%を達成し、出力電力32mWを実現することに成功しました。

図4 再配線技術を適用したパワーアンプモジュール写真

効果

CMOSと再配線技術を組み合わせた実装技術を開発し、パワーアンプの高出力化を実現しました。課題となっていたパワーアンプをCMOSチップで作成可能とすることにより、すべてのミリ波RF回路をCMOSで実現することが可能となります。これにより、RF送受信ICを小型・低コストに作成し、安価なミリ波アプリケーションを提供することが期待されます。

今後

今回開発した技術を応用し、パワーアンプ以外のミリ波帯RF回路の接続にも広範囲に適用し、低コスト、小型な無線通信モジュールを開発していきます。

商標について

記載されている製品名などの固有名詞は、各社の商標または登録商標です。

以上

注釈

- 注1 株式会社富士通研究所:

- 代表取締役社長 富田達夫、本社 神奈川県川崎市。

- 注2 車載レーダー:

- 電波の送受信により自車周辺の車との距離と角度、相対速度を計測するシステム。

- 注3 ミリ波:

- 波長1~10mm(周波数30~300GHz)の電磁波。

- 注4 CMOS技術:

- シリコン基板上に作成された、N型とP型のMOS(Metal Oxide Semiconductor)トランジスタを相補的に接続して構成されている半導体技術。消費電力が小さく、現在の集積回路の主流となっている。

- 注5 化合物半導体:

- 2種類以上の元素からなる半導体で、GaAs(ガリウムヒ素)、InP(インジウムリン)などがある。シリコンに比べて電子の移動度が高いため、高速動作が可能。

本件に関するお問い合わせ

株式会社富士通研究所

基盤技術研究所

![]() 046-250-8244 (直通)

046-250-8244 (直通)

![]() cmos_rdl@ml.labs.fujitsu.com

cmos_rdl@ml.labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。