PRESS RELEASE (技術)

2009年2月13日

株式会社富士通研究所

Fujitsu Laboratories of America, Inc.

富士通株式会社

40Gbps光伝送システム向けCMOS送信ICの開発

~世界初! 65nm標準CMOS技術で、40Gbps送信ICの全機能を1チップに集積化~

株式会社富士通研究所(注1)、Fujitsu Laboratories of America, Inc.(注2)、および富士通株式会社は、65ナノメートル(以下、nm)世代の標準CMOS技術(注3)を用いて、毎秒40ギガビット (以下、40Gbps)の基幹系光伝送システム向け送信ICを開発しました。

送信に必要な信号生成回路を40Gbpsに高速化すると同時に、実用上求められる電源電圧の変動範囲内で、40Gbpsの安定した出力信号が生成できる新しい回路技術を開発しました。さらに40Gbps送信に必要な入出力インターフェース(注4)、信号処理(注5)、高速信号生成(注6)の機能全てを1チップに集積させた光伝送システム向け送信ICを、CMOS技術により世界で初めて実現しました。40Gbpsの送信ICとしては今までにない多機能性を1チップに集積化したことにより、光伝送システムの低消費電力化、小型化、低コスト化に大きく貢献します。

今回の技術の詳細は、米国 サンフランシスコで2月8日から開催された国際固体素子回路会議ISSCC(IEEE International Solid-State Circuits Conference)にて発表しました。(発表番号21.2)

なお、本研究の一部はNEDO(独立行政法人 新エネルギー・産業技術総合開発機構)の委託(次世代高効率ネットワークデバイス技術開発)を受けて、財団法人 光産業技術振興協会において実施したものです。

背景

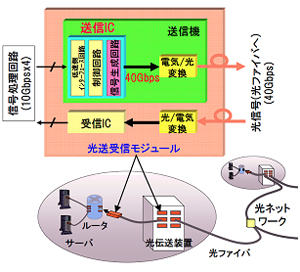

図1 光伝送システムの構成図 |

ブロードバンドネットワークの普及にともなって増加する通信トラフィックに対応するため、基幹系のネットワークにおいて40Gbpsの高速伝送を実現する光伝送システムの導入が進んでいます。40Gbps光伝送システムのさらなる普及のために、光信号を中継する光伝送装置の低消費電力化、小型化、低コスト化が求められています。

光伝送装置を構成する送信機では、2.5~10Gbps程度の速度で入力される複数の低速電気信号を多重化して、40Gbpsの高速電気信号を出力する送信ICが必要です。現在、送信ICにおいて、低速側インターフェース回路や内部の制御回路はCMOS技術で作製されていますが、40Gbpsの高速電気信号の信号生成回路は、高速特性に優れる化合物半導体(注7)で作製する必要がありました(図1)。微細化にともない高速で動作するようになったCMOS技術で信号生成回路を作製し、送信機の全ての機能をCMOS技術で1チップに集積できれば、光伝送装置の低消費電力化、小型化、低コスト化が可能になります。

課題

CMOS技術により、信号生成回路の高速動作を可能とし、化合物半導体と同品質の40Gbps出力波形を実現するためには、データを伝送する回路の動作速度を向上させるだけでなく、回路動作のタイミングを決定するために回路に供給されるクロック信号に関して20GHzで低ノイズかつ十分な振幅を確保することも重要です。回路中でクロック信号の振幅が劣化する大きな要因の一つとして、配線や素子に付随する寄生容量(注8)による損失があります。化合物半導体に比べて寄生容量が大きいCMOS技術において、20GHzのクロック信号の振幅劣化を抑制するためには、寄生容量の影響をいかに抑圧するかが大きなポイントになります。

また、微細化によりトランジスタの高速性能が向上する一方、トランジスタの耐圧が低下するため、使用可能な電源電圧が1~1.2ボルト(以下、V)と低電圧に制限されます。このため、供給される電源に変動が生じると、回路に十分な電源電圧が供給されず、動作が不安定になります。光伝送システムの低コスト化のためには、このような使用条件の変化に対して、回路内でのデータ信号とクロック信号のタイミング関係を一定に保ち、安定に動作する回路を実現することも課題となります。

開発した技術の概要

今回、40Gbpsに高速化すると同時に、製品に求められる温度や電源電圧の範囲内の全条件で、40Gbpsの安定した出力信号が生成できる以下の回路技術を、世界で初めて開発しました。

- クロック信号伝送技術

今回、送信IC内のクロック伝送回路に低消費電力で低ノイズのクロック伝送を可能とする新しいインダクタ(注9)補償技術を開発しました。

一般的に寄生容量の影響を抑圧するためには、容量と逆の特性を示すインダクタによる特性補償が用いられます。送信IC内のクロック信号が単一周波数であることに着目し、クロック信号の周波数に近い領域のみインダクタで寄生容量を補償する新しい高速化技術を適用することで、従来に比べて少ない回路段数でノイズの少ない高速クロック信号伝送を可能としました。

- 自動タイミング調整技術

回路動作を制御するクロック信号と回路を通過するデータ信号のタイミングを常に監視し、相互の信号の関係が最適になるように、動的に調整する新しい回路技術を出力回路に適用しました。この回路技術では、監視、調整する機構を、データ信号の伝達経路から分離した構成を採用することで、監視、調整回路の追加によるデータ信号の波形の劣化を引き起こすことなく、自動的に相互の信号のタイミングを最適化し、高速で安定した波形の送信が可能です。

効果

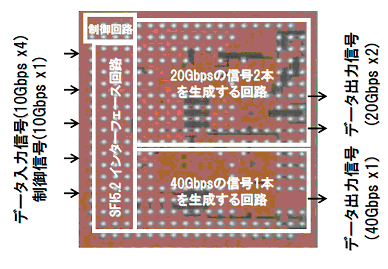

上記技術を適用して、信号生成回路をCMOS技術で実現し、低速側インターフェース回路、制御回路などを整合させて集積することにより、世界で初めて、40Gbps送信ICを標準65nm CMOS技術を用いて1チップで実現しました。(図2)

|

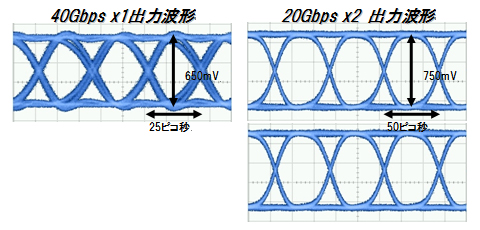

開発技術を適用した送信ICの出力波形は、図3のように安定しており、実用上求められる電源電圧の変動範囲で、確実に"0"と"1"が判定可能な40Gbps出力信号が生成できることを確認しました(データ誤り率10-12以下、すなわち1兆個のデータに対して1個以下の誤り)。この結果、本技術が、電源電圧の変動だけでなく、送信ICの使用温度の変化による影響に対しても有効であることを確認しました。

また、1チップ集積化、新規クロック伝送回路の採用などにより、消費電力を2W以下におさえ、従来の3分の1以下に低減しました。低消費電力化により発熱を抑えられるため、光伝送装置内への光送受信モジュールの高密度な実装が可能となります。今回の開発により、従来の40Gbps光伝送装置と比較して、約2分の1の小型化が可能となり、装置全体の低コスト化が可能になります。

本送信ICは、低速側インターフェースに近年標準化されたSFI5.2(注10)インターフェースを世界で初めて採用しています。また、CMOS技術の高集積化のメリットを活かし、長距離伝送のための信号変調方式に対応する20Gbpsの信号2本を出力する機能を付加しています(図2)。CMOS技術を用いた送信ICの実現により、1チップで複数システムへの対応が可能となり、今後の40Gbps光伝送装置の普及が期待できます。

|

今後

今回開発した、送信ICに関して40Gbps出力波形のさらなる改善を行ないます。また、CMOS技術を用いた受信ICの開発を進め、光伝送装置の小型化に貢献する予定です。また、今回開発した成果は、基幹系光伝送システムだけでなく、将来的にはLANや企業ネットワークの高速化の実現に向け、40Gbpsイーサーネットシリアル光伝送装置などに展開していきます。

以上

注釈

- 注1 株式会社富士通研究所:

- 代表取締役社長 村野和雄、本社 神奈川県川崎市。

- 注2 Fujitsu Laboratories of America, Inc.:

- 代表取締役社長 松本均、米国カリフォルニア州、株式会社富士通研究所の米国拠点。

- 注3 CMOS技術:

- シリコン基板上に作成された、N型とP型のMOS(Metal Oxide Semiconductor)トランジスタを相補的に接続して構成されている半導体技術。消費電力が小さく、現在の集積回路の主流となっている。

- 注4 入出力インターフェース:

- I2C制御を用いて、入出力信号の論理や順番、送信ICの動作モードなどを切り替えられる機能を指す。

- 注5 信号処理:

- 10Gbpsの電気信号5本をデータ誤りなく受信するためのデータリカバリ機能や、これら5本の信号の間のタイミング誤差を吸収し、同一のタイミングに揃えるための機能を指します。

- 注6 高速信号生成:

- 受信した10Gbpsの電気信号から、20Gbpsの電気信号2本、または40Gbpsの電気信号1本を生成する機能を指す。

- 注7 化合物半導体:

- 2種類以上の元素からなる半導体で、SiGe(シリコンゲルマニウム)、GaAs(ガリウムヒ素)、InP(インジウムリン)などがある。純粋なシリコン半導体に比べて電子の移動度が高いため、高速動作が可能。

- 注8 寄生容量:

- トランジスタ素子の入出力電極や、その周辺に配置されたその他の素子の電極との間に形成される静電容量。素子の電極の大きさや素子間の距離によってその値が変化するため、回路図上に表現できない。

- 注9 インダクタ:

- 周波数が高くなると、電気が通りにくくなる素子。半導体上では、一般的に渦巻状の配線パターンで作られている。

- 注10 SFI5.2:

- Serdes Framer Interface Level 5 Phase 2の略。OIF(Optical Internetworking Forum)により2006年10月に定められた規格。

関連リンク

本件に関するお問い合わせ

株式会社富士通研究所

システムLSI開発研究所 ネットワークSOC開発部

電話: 044-754-2692 (直通)

E-mail: 40g_pr@ml.labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。