PRESS RELEASE (技術)

2008-0250

2008年12月16日

株式会社富士通研究所

32nm世代以降の低消費電力化CMOS技術を開発

~既存の製造設備を活用して消費電力を20%削減~

株式会社富士通研究所(注1)は、32ナノメートル(以下、nm)世代以降のロジックLSI向けに、低消費電力化CMOS技術(注2)を開発しました。本技術は、従来、性能が低く基板の表面に適用されていなかったシリコンの特定の結晶面(注3)を用いて、その性能を向上させるものです。これにより、世界で初めて、45nm世代の既存の製造設備を利用することによりコストの増加を抑制しながら、LSIの動作速度を落とさずに電源の電圧を下げることができ、動作時の消費電力を約20%削減します。本技術は、今後ますます多機能化が要求される各種携帯機器向けのシステムLSIや、マルチコア化が進むマイクロプロセッサなどへの幅広い適用が見込まれます。

なお、本技術の詳細は、米国サンフランシスコで12月15日から開催されている半導体の国際会議「2008 IEEE International Electron Devices Meeting (IEDM)」にて発表しました。(講演番号3.3)

背景

携帯機器の多機能化や高性能サーバの高速化などが進む反面、消費電力の増大が問題になっています。ロジックLSIの低消費電力化には、一般的に電源の電圧の低減が有効です。ただし、単に電源の電圧を下げるだけではMOSトランジスタが流すことができるオン電流(注4)が減少し、動作速度の低下を招きます。このため、電圧を下げてもオン電流を維持する技術が必要となります。この課題に対し、さまざまな歪技術(注5)が検討されてきましたが、45nm世代で歪技術の改良はほぼ限界まできています。

32nm世代以降では、同じ電圧で比べた場合にオン電流をさらに向上させる技術として、High-k技術 (注6)やメタルゲート技術(注7)が有力視されています。一方、基板の表面にシリコンのどの結晶面を適用するかで物性が変化するため、基板表面の結晶面を見直すことによりオン電流を向上させる研究が活発に行われています。

課題

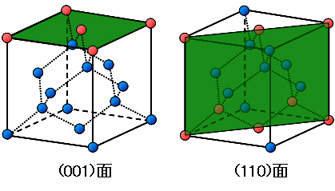

現在、シリコン基板の表面は NMOSトランジスタ(以下、NMOS)の移動度が高い(001)面(図1)が主流となっています。しかし、45nm世代まで使用していた既存の製造設備では、 (001)面のオン電流を向上させることは難しくなっています。これに対して、(110)面(図1)は、PMOSトランジスタ(以下、PMOS)の移動度が(001)面よりも高くなることから注目されていますが、NMOSの移動度が(001)面よりも低いといった問題がありました。このため、「NMOSのオン電流+PMOSのオン電流」の合計は(001)面の方が大きくなり、(110)面の基板への適用は実用化されませんでした。(110)面を基板とした低消費電力ロジックLSIの実用化には、製造コストの増加を最小限に抑えながら、NMOSのオン電流を(001)面と同等レベルに向上させる必要があります。

|

技術の概要

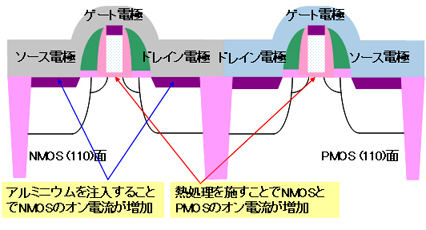

今回、世界で初めて、既存の45nm世代の製造設備で(110)面のシリコン基板を適用しながら、(001)面と比較してNMOSのオン電流を減少させることなく、PMOSのオン電流を向上させることが可能な32nm世代向けの新技術を開発しました。(図2)

|

- シリコンの表面処理技術

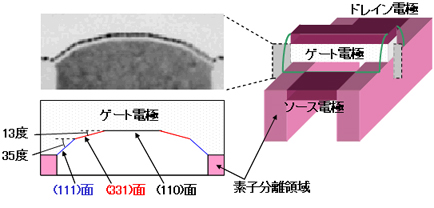

ゲート絶縁膜形成前に熱処理を施すことで、シリコンとゲート絶縁膜の界面形状が変形します。通常と異なる特殊なガスの中で熱処理を施すことで、素子分離領域(注8)近傍に (111)面と(331)面を形成することに成功しました。(図3)

(111)面および(331)面のNMOSの移動度は(110)面の移動度よりも高いことから、ゲート中央部は(110)面のままであっても、オン電流は10%の向上を実現することができました。同時にPMOSのオン電流も移動度の向上により10%の向上を実現させました。

図3 トランジスタのゲート幅方向の断面と結晶面の関係 - シリサイド(注9)へのアルミニウム注入技術

シリサイド形成後にアルミニウムを注入することにより、NMOSのシリサイドとシリコンのコンタクト抵抗(注10)が減少することを見出しました。アルミニウムをシリサイドの極浅領域に注入することで、NMOSのオン電流を20%向上させました。さらに、シリコンの表面処理技術と併用することで、(110)面のシリコン基板を用いても、(001)面と同等のNMOSのオン電流を実現させました。

一方、PMOSのコンタクト抵抗はアルミニウムの注入により増加し、PMOSのオン電流が減少することが分かりました。そこで、NMOS領域に選択的にアルミニウムを注入するプロセスを構築し、PMOSのオン電流の減少を防ぎました。

効果

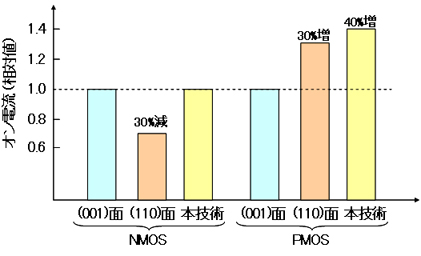

本技術を適用し(110)面のシリコン基板のLSIを試作した結果、従来の(001)面のシリコン基板を用いる場合に比べて、NMOSのオン電流を維持したまま、PMOSのオン電流を40%向上させることができました。 (図4) これにより、電源の電圧を10%下げても動作速度は低下せず、この電圧の低下により動作時の消費電力を約20%削減できました。

また、本技術を既存の45nm世代の製造工程に導入した場合、追加される工程は熱処理とイオン注入の2工程のみです。さらに、32nm世代以降の製造工程に本技術を導入した場合でも、ウェーハコストを除いた製造コスト増大は1%以下に抑えることが可能です。

|

今後

32nm世代以降での多機能化が要求される各種携帯機器向けのシステムLSIや、マルチコア化が進むマイクロプロセッサなどへの幅広い適用のために、実回路での評価を進めていきます。

以上

注釈

- 注1 株式会社富士通研究所:

- 代表取締役社長 村野和雄、本社 神奈川県川崎市。

- 注2 CMOS技術:

- 電荷の運搬に電子を用いるNMOSトランジスタと電子の欠落部分である正孔を用いるPMOSトランジスタをシリコン基板上に混載して製造する技術。動作速度を上げるためには両トランジスタの性能を向上させる必要がある。

- 注3 結晶面:

- 結晶の原子配列の方向を意味する。シリコンのような結晶は立方体となるため、面の向きをx、y、z軸に対応させて表現する。シリコンに関しては主に(001)面、(110)面、(111)面の物性が研究されてきた。

- 注4 オン電流:

- トランジスタがオン状態の時に流れる電流。チャネル(ゲート下部)の移動度と電子(または正孔)を増やすことと、寄生抵抗を減らすことでオン電流が増加する。オン電流が大きいほど動作速度が速くなる。

- 注5 歪技術:

- トランジスタにストレスを加えて移動度を向上させる技術。

- 注6 High-k技術:

- ゲート絶縁膜にシリコン酸化膜よりも高誘電率の材料を使い、チャネルの電子(または正孔)を増やす技術。

- 注7 メタルゲート技術:

- ゲートに金属を用いることで、従来のポリシリコンで課題となっていたゲート絶縁膜との界面に形成される空乏層の拡がりを抑制し、チャネルの電子(または正孔)を増やす技術。

- 注8 素子分離領域:

- 個々のトランジスタを電気的に分離する領域。

- 注9 シリサイド:

- シリコンと高融点金属との化合物。ロジックLSIでは寄生抵抗を減らすために広く使われている。

- 注10 コンタクト抵抗:

- シリコンとシリサイドの接触抵抗。現在のトランジスタはコンタクト抵抗を削減することで寄生抵抗が減少し、オン電流が向上する。

関連リンク

本件に関するお問い合わせ

株式会社富士通研究所

R&D戦略室

電話: 044-754-2614 (直通)

E-mail: silicon-ask@ml.labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。