PRESS RELEASE (技術)

2008年6月17日

株式会社富士通研究所

富士通マイクロエレクトロニクス株式会社

システムLSIの低電力化を実現する電源遮断技術を開発

~世界初!1マイクロ秒以内の高速で電源をオン状態へ~

なお、本技術の詳細は、6月18日から20日、米国ホノルルで開催される「2008 Symposium on VLSI Circuits」で発表する予定です。

開発の背景

LSIの高集積化が進むほど、リーク電流(注3)が増大します。特に携帯電話は電源オン状態のまま回路が処理を行わない待機時間が長く、リーク電流の影響を受けやすいため、消費電力を増加させ、電池寿命を縮める要因になります。このリーク電流を抑制するために、回路を使用しない時間帯では電源をオフ状態にするという電源遮断技術が用いられています。従来の電源遮断技術では、電源オフ状態からオン状態へ復帰する際、数マイクロ秒にわたる長い復帰時間を要します。復帰時間が長くなるほど電源オフの時間が短くなり、リーク電流を抑制できないばかりか、復帰時間中は回路を使用できないため、システム性能の劣化も招いてしまいます。

次世代モバイル機器では1マイクロ秒以内の復帰時間が求められますが、従来の電源遮断技術では不可能でした。

課題

電源をオン状態に復帰するためには、回路の再充電が必要です。従来技術では、回路充電時に流れ込む電流(突入電流)を弱いスイッチで抑制し、回路の充電が終了次第、本来の電流供給力を持つ強いスイッチを高速に復帰させ、全体として高速化するというものでした。しかし、1マイクロ秒以内の回路の高速復帰を行うために、突入電流を増加させると、内部回路動作に悪影響を及ぼす大きな電源ノイズ(注4)を招くという問題が発生します。

このため、電源ノイズを数ミリボルトに抑制するには、電源を供給する配線(以下、電源線)のインピーダンス(注5)を下げることで突入電流の影響を低減する必要がありますが、実際のLSIの適用においては大幅なコスト増を招くため実現が難しいとされています。

開発した技術

今回開発した技術は、富士通マイクロエレクトロニクスの電源遮断技術を発展させたもので、電源の高速復帰を実現しながら、同時に突入電流による電源ノイズを抑制することが可能です。

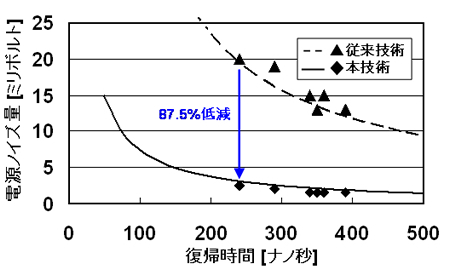

従来技術の突入電流を抑制するための弱いスイッチに対してバイパス専用の電源線を設け、さらにそのスイッチの制御手順を最適化する方式を開発しました。この方式を採用することにより、突入電流によるバイパス専用の電源線のノイズは、動作中の他の回路が接続されている主電源線へ回り込まなくなります。このため、突入電流による主電源線の電源ノイズは電源インピーダンスを下げなくても従来の4分の1以下に抑制できます。許容される電源ノイズの量が同じなら、従来の4分の1以下に復帰時間の高速化が可能となります。

効果

今回、90ナノメートル(以下、nm)プロセスで製造した200万ゲートの回路規模を持つデュアルコアプロセッサで評価実験を行いました。その結果、復帰時間が240ナノ秒の状況下で、従来技術では主電源線の電源ノイズは20ミリボルト検出されましたが、本技術では2.5ミリボルトに抑制(87.5%低減)されていることを実測で確認しました(図)。これは従来技術で達成が難しかった1マイクロ秒以下の電源復帰時間の実現が可能であることを示しています。

さらに、バイパス専用電源線などの追加設置によるチップ面積の増加分は1%未満と、チップ面積をほとんど増加させる必要がありません。

|

今後

今後、本技術を、富士通マイクロエレクトロニクスが体系化している省電力技術「CoolAdjust(注6)」のひとつとして、65nmおよび45nm CMOSテクノロジーの標準LSI設計フローへの組み込み、ASSP(注7)やASIC(注8)などに適用していく予定です。

以上

注釈

- 注1 株式会社富士通研究所:

- 代表取締役社長 村野和雄、本社 神奈川県川崎市。

- 注2 富士通マイクロエレクトロニクス株式会社:

- 代表取締役社長 岡田晴基、本社 東京都新宿区。

- 注3 リーク電流:

- 回路が停止している間でも漏れ出す無駄な電流のこと。

- 注4 電源ノイズ:

- LSI内部回路動作に悪影響を及ぼす電源の電圧変動のこと。

- 注5 インピーダンス:

- 配線に電流を供給する際の電流の流れにくさの度合いを表したもの。単位はオーム(Ω)。

- 注6 CoolAdjust:

- 富士通マイクロエレクトロニクスの電源制御による省電力化技術。電源遮断技術の他、プロセスや温度変動に応じて最適な電源電圧や基板電圧を供給する技術などで構成される。

- 注7 ASSP:

- Application Specific Standard Productの略。特定分野向けに機能特化した汎用LSI。

- 注8 ASIC:

- Application Specific Integrated Circuitの略。特定用途向け専用LSI。

関連リンク

本件に関するお問い合わせ

株式会社富士通研究所

システムLSI開発研究所 SOC設計技術研究部

電話 : 044-754-2657(直通)

E-mail : lp-pg@ml.labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。