PRESS RELEASE (技術)

2007-2048

2007年12月14日

株式会社富士通研究所

バラツキを抑制した高速低消費電力ReRAMの開発に成功

株式会社富士通研究所(注1)は、次世代の不揮発性メモリ(注2)の一つである、ReRAM(抵抗メモリ)(注3)の低消費電力化と抵抗値のバラツキを低減させることに成功しました。今回、ReRAM素子の構造を、チタン(Ti)を添加した酸化ニッケル(NiO)に変更し、トランジスタによる電流制限をかけることにより、メモリ消去時に必要となる電流を100マイクロアンペア(μA)以下に低減しました。また、5ナノ秒(以下、ns)という高速の消去動作においても、素子の品質に影響を及ぼす抵抗値のバラツキを約10分の1に低減させました。今後、フラッシュメモリ代替として高速、低消費電力、低コストの混載メモリ(注4)を目指します。

なお、今回の技術については、米国ワシントンD.C.で12月10日から開催されている半導体の国際学会、IEDM(International Electron Devices Meeting )にて発表しました(講演番号30.1)。

開発の背景

現在、システムLSIでは、フラッシュマイコンのように、ROM(読み出し専用メモリ)ではなくフラッシュメモリのような不揮発メモリを混載することで、ソフトウェアを後から書き換えられるものが主流となってきています。しかし、フラッシュメモリは、近い将来、微細化の限界に達すると予想されており、その代替となる各種のメモリの研究が行われています。

ReRAMは、電圧を加えることで抵抗の値が変化する材料を素子として用いたメモリです。ReRAMは、微細化に適していること、製造コストが低いことから、フラッシュメモリ後継の一つとして注目されています。

課題

ReRAMは、メモリ消去時に必要となる電流の低減が重要となります。また、高速で書き込みや消去を繰り返し行なった場合、抵抗の値にバラツキが生じ、品質に影響を及ぼすことが知られています。

今回開発した技術

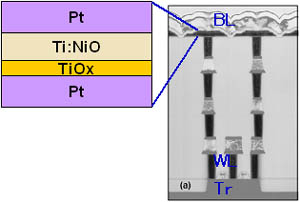

図:今回開発したReRAM素子(左)とトランジスタを組み合わせた構造(右) |

従来、ReRAM素子には酸化ニッケル(NiO)膜が用いられていました。今回、NiO膜に新たにチタン(Ti)を添加した膜(Ti:NiO)による素子構造を開発し、トランジスタと組み合わせて性能を評価しました。(図)

その結果、メモリ消去時の電圧を高くすることが可能になり、従来の約1万倍の5nsに高速化させることに成功しました。また、同時に、抵抗値のバラツキを約10分の1に低減しました。また、トランジスタにかける電圧を最適化することにより、メモリ消去時に必要となる電流を100μA以下に低減しました。

効果

新たな材料を用い、高速動作においても抵抗値のバラツキの少ないReRAM素子を試作しました。フラッシュメモリ代替として、より微細な不揮発性メモリをReRAMで実現することができれば、携帯機器などのさらなる高性能化が見込まれます。

今後

ReRAM素子の微細加工技術の開発、読み出し・書き込み回路の設計など、ReRAMの研究開発を推進していきます。

以上

注釈

- 注1 株式会社富士通研究所:

- 代表取締役社長 村野和雄、本社 神奈川県川崎市。

- 注2 不揮発性メモリ:

- 電源を切っても内容を保持できるメモリ。

- 注3 ReRAM (抵抗メモリ):

- Resistive Random Access Memory。記憶素子に電界を加えた際に生じる巨大な抵抗変化を利用するメモリ。

- 注4 混載メモリ:

- システムLSIに搭載されるメモリ。

関連リンク

本件に関するお問い合わせ

株式会社富士通研究所

シリコンテクノロジ開発研究所 混載メモリ開発部

電話: 046-250-8379(直通)

E-mail: emd-si@ml.labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。