PRESS RELEASE (技術)

2017年4月24日

株式会社富士通研究所

Deep Learningの学習用ハードウェアの電力効率を向上させる回路技術を開発

株式会社富士通研究所(注1)(以下、富士通研究所)は、Deep Learningの学習処理に用いるデータのビット幅を削減することで、ニューラルネットワーク構造や学習方式を変えずに学習用ハードウェアの電力効率を向上させる回路技術を開発しました。

Deep Learningの学習プロセスでは学習データをもとに膨大な演算処理を行う必要がありますが、学習処理を実行するサーバなどのハードウェアでは利用できる電力量で処理性能の上限が決まることから、Deep Learningの学習処理を高速化するためには、電力効率を向上させることが課題となっていました。

今回、演算に用いるデータのビット幅を削減した独自の数値表現と、Deep Learningの学習演算の特徴をもとに、演算器の動きを随時解析しながら学習に必要十分な演算精度を保つように小数点の位置を自動的に制御する演算アルゴリズムによる回路技術を開発しました。これにより、Deep Learningの学習過程において、演算器のビット幅や学習結果を記録するメモリのビット幅を削減でき、電力効率を向上させることが可能となります。

本技術を実装したDeep Learning学習用ハードウェアを想定したシミュレーションにおいて、LeNet(注2)を用いた学習の例では、32ビットの演算器で行った場合と比較して演算器やメモリの消費電力を約75%削減できるなど、電力効率を大幅に向上できることを確認しました。これにより、クラウド上のサーバやエッジサーバなど様々な場所で、大規模なDeep Learning処理による高度なAI技術の適用領域の拡大が可能になります。富士通研究所では本技術を、富士通株式会社のAI技術「Human Centric AI Zinrai(ジンライ)」の一つとして実用化を目指します。

本技術の詳細は、4月24日(月曜日)から4月26日(水曜日)まで虎ノ門ヒルズフォーラム(東京都港区)で開催される「xSIG 2017(The 1st. cross-disciplinary Workshop on Computing Systems, Infrastructures, and Programming)」にて発表する予定です。

開発の背景

近年、IoTの普及に伴ってネットワークに接続されるデバイスが急増しており、2020年までに数百億個のデバイスが接続され、膨大なデータが生成されると言われています。これらの大量のデータは、そのままでは意味を持たない場合が多く、Deep Learningなどの機械学習によって価値を抽出し、新たな知見を創出することが期待されています。

IoTによる学習データの増大と、Deep Learningのニューラルネットワーク大規模化により、学習用サーバへの性能要求はますます増大する傾向にあります。また、データを転送するための通信量やデータを記録するためのストレージ量を減らすために、クラウドだけではなくデータが生成される場所に近いエッジ側で学習を行いたいというニーズもあります。

これらエッジ、クラウド双方のDeep Learningの学習用サーバはそれぞれ電力的な制限があるため、今後、単純に規模を拡大して高性能化することは難しくなることが想定され、電力効率を高める技術が必要とされています。

課題

一般的にDeep Learningの学習に用いられているハードウェアでは32ビットの浮動小数点と呼ばれるデータ形式で演算処理を行っています。これを16ビットやそれ以下のビット幅にするなど演算に使うデータのビット幅を削減したり、整数で演算を行うハードウェアを用いることで、演算量を削減し、電力効率を高めることができますが、一方で演算の途中で演算に必要な精度が不足し、学習ができなくなったり、Deep Learningの認識性能が劣化してしまうことがありました。

開発した技術

今回、整数演算を基にして、Deep Learningの学習プロセスに特化してビット幅を削減した独自の数値表現と、多層ニューラルネットワークの層ごとに演算中のデータを随時解析しながら演算精度を保つように小数点の位置を自動的に制御する演算アルゴリズムにより、Deep Learningの学習過程において、演算器のビット幅や学習結果を記録するメモリのビット幅を削減して電力効率を向上させる回路技術を開発しました。

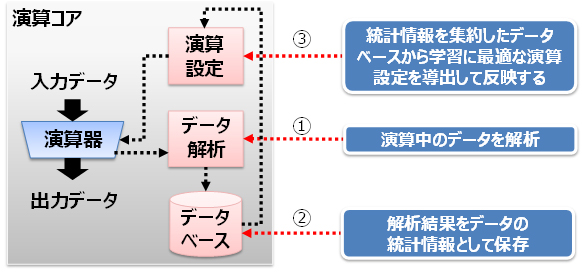

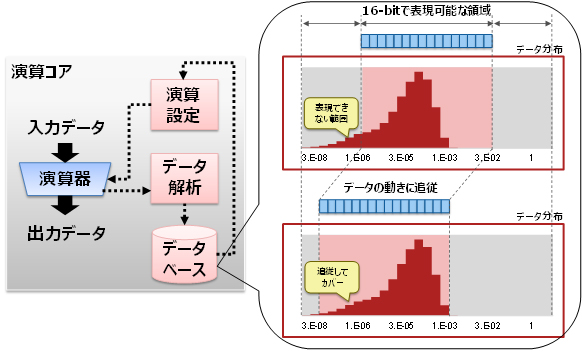

本技術を用いたDeep Learningの学習用ハードウェアの演算コアには、①演算中のデータを解析するブロック、②解析したデータの分布を保存するデータベース、③演算の設定を保持するブロックを持ちます(図1)。データ解析ブロックでは、Deep Learningの学習中に演算器の出力データをリアルタイムに解析して、データ分布を表す統計情報としてデータベースに保存し、その分布から、Deep Learningの学習精度を向上させるために十分な演算精度を保つことができるように学習に最適な設定をして演算を進めます(図2)。

図1 演算コアによる演算精度の向上

図2 統計情報を用いた演算設定の最適化

効果

開発した回路技術は、2つの側面から電力効率を向上させることが可能です。1つは、浮動小数点で行われていた演算を整数で行うことで、消費電力を削減(注3)することができます。また、32ビットから8ビットにビット幅を削減することで、演算器やメモリの消費電力を約75%削減することになります。本技術を実装したDeep Learning学習用ハードウェアを想定したシミュレーションにおいて、LeNetとMNIST(注4)のデータセットを用いて学習を行ったところ、32ビット浮動小数点演算での学習結果では98.90%の認識率に対し、16ビットで98.89%、8ビットで98.31%の認識率で学習できることを確認しました。このように、Deep Learningの学習向けハードウェアの電力効率を向上させることで、大量の学習データを必要とするDeep Learning学習処理をクラウドサーバから、データが生成される場所に近いエッジサーバに適用していくことを可能にします。

今後

富士通研究所では、開発した技術を富士通株式会社のAI技術「Human Centric AI Zinrai(ジンライ)」の一つとして2018年度の実用化を目指し、お客様とともにAIの活用に取り組んでいく予定です。また、Deep Learningの学習に用いるデータ量をさらに削減するための回路技術の開発を進めます。

商標について

記載されている製品名などの固有名詞は、各社の商標または登録商標です。

以上

注釈

- 注1 株式会社富士通研究所:

- 本社 神奈川県川崎市、代表取締役社長 佐々木繁。

- 注2 LeNet:

- 手書き数字認識によく使われる畳み込みニューラルネットワーク。

- 注3 浮動小数点で行われていた演算を整数演算で行うことで、消費電力を削減:

- 浮動小数点で行われていた演算を整数演算で行うことで、電力を削減:例えば、32ビット整数データの乗算器と加算器の電力は合計約3.2ピコジュール(pJ)、32ビット浮動小数点データでは約4.6pJというデータがあり、この場合、演算器の電力を約30%削減することができる。出典:M. Horowitz, "1.1 Computing's energy problem(and what we can do about it)," 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers(ISSCC), San Francisco, CA, 2014, pp. 10-14.

- 注4 MNIST:

- 28x28ピクセルの手書き数字認識用の学習データセット。

本件に関するお問い合わせ

株式会社富士通研究所

コンピュータシステム研究所

![]() 044-754-2931(直通)

044-754-2931(直通)

![]() ngcs_ai_press_arc@ml.labs.fujitsu.com

ngcs_ai_press_arc@ml.labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。