PRESS RELEASE (技術)

2015年2月23日

富士通株式会社

株式会社富士通研究所

Fujitsu Laboratories of America, Inc.

技術研究組合 光電子融合基盤技術研究所

独立行政法人 新エネルギー・産業技術総合開発機構

CPU間の高速伝送を世界最小の1Gbpsあたり5mWで実現

シリコンフォトニクス技術を用いて従来の半分の電力で高速伝送に成功

富士通株式会社(注1)(以下、富士通)、株式会社富士通研究所(注2)(以下、富士通研究所)、Fujitsu Laboratories of America, Inc.(注3)(以下、FLA)、技術研究組合 光電子融合基盤技術研究所(注4)(以下、PETRA)、独立行政法人 新エネルギー・産業技術総合開発機構(注5) (以下、NEDO)は、サーバやスパコンのCPU間高速データ通信を世界最高の電力効率である1Gbps(注6)あたり5mWで実現するシリコンフォトニクス技術(注7)を用いた光送受信回路を共同開発しました。

従来、光素子を高速に動作させるためには、光素子に一定の電圧をかける必要があり、光送受信回路の省電力化は困難でした。今回、光素子を低電圧駆動させながら、送信データの変化を捉えて大きな振幅になるように補い、従来の半分の電力で25Gbpsの高速動作を実現しました。

本技術により、消費電力を抑えながら、複数の光送受信回路を並べた毎秒テラビット級の高速伝送を実現できるため、サーバやスパコンの高性能化が期待されます。

本技術の一部は、NEDOよりPETRAに委託された「超低消費電力型光エレクトロニクス実装システム技術開発」プロジェクトによるもので、富士通は富士通研究所、およびFLAとともに送受信回路技術を開発しています。

本技術の詳細は2月22日(日曜日)から米国サンフランシスコで開催される半導体技術に関する最大級の会議である国際会議「国際固体素子回路会議ISSCC 2015(IEEE International Solid-State Circuits Conference 2015)」で発表します(ISSCC発表番号22.2)。

開発の背景

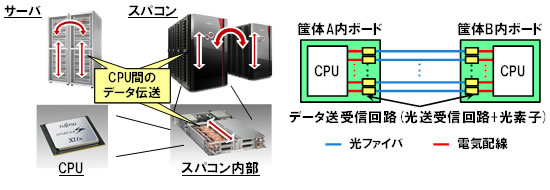

CPUを多数接続した大規模システムであるサーバやスパコンでは、高性能化に伴いCPUが搭載された筐体内や筐体間での通信データ量がますます増加しています。このため、サーバやスパコンの性能向上には、CPU単体の演算性能を高めるだけでなく、それらをつなぐCPU間のデータ通信速度の向上も重要です。サーバやスパコンではシステム全体で大きな電力を必要としますが、設備が供給できる電力の制約から、データ送受信回路の電力を増やすことなく通信速度を向上させることが求められています。

次世代の高性能スパコンで期待されているシリコンフォトニクス技術を用いた光送受信技術では、光素子の実用的な伝送速度の限界が25Gbpsであることから、光素子とそれを駆動する電子回路の光送受信回路を複数並べ、全体として高速化を図る方法が考えられます。一方、CPU間データ通信は4年で2倍の高速化が求められており、電力一定のもとで高速化を実現するには、光送受信回路の電力を半分にする必要があります(図1)。

図1 高性能サーバやスパコンのCPU間データ通信

課題

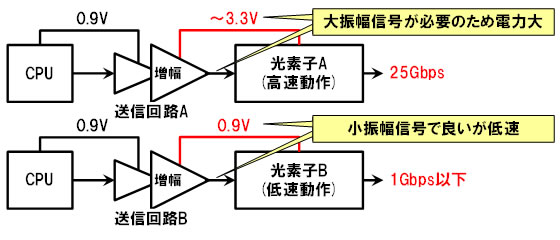

25Gbpsの高速な光送受信では一般的に、CPUなどの電子回路が必要とする電源電圧0.9ボルト(V)に比べて高い3V以上の電源電圧で光素子を動作させています。光素子を駆動する送信回路も高い電源電圧で動作させ、光素子に常に振幅の大きな信号を送ることで高速動作を実現するため、低消費電力化が困難という課題がありました。また、低消費電力化のため、CPUと同じ0.9Vの低い電源電圧で動作する光素子を用いる場合、1Gbps程度の低速動作しか実現できないという問題もあります(図2)。

図2 光送受信回路の課題

開発した技術

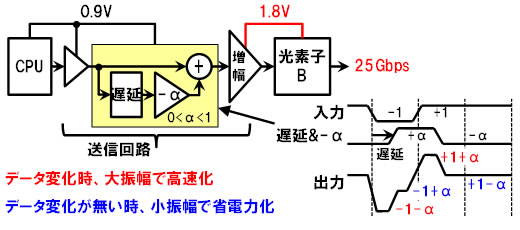

今回、CPUからの送信信号が-1や+1に変化するタイミングに限定して増幅することで、1.8V程度の振幅を断続的に発生させることに成功しました。これにより、電源電圧が1.8Vと3.3Vに比べて低く、データが変化しないところは小振幅で電力を使わないため、低消費電力を実現しています。

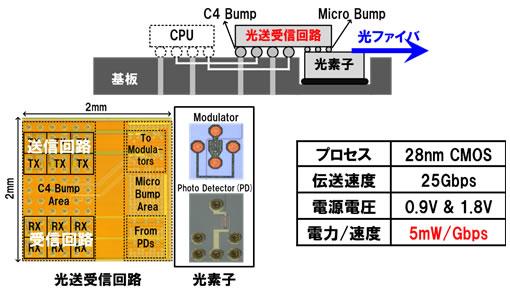

原理的には、送信データとそれを遅延させたデータを-α(0<α<1)倍したものを足し合わせることで、送信データが-1から+1へ変化する場合、+1が+1+αに増幅されます。また、送信データが+1から-1へ変化する場合、-1が-1-αとマイナス方向にさらに変化させることができます(図3)。本技術により、高速化と低消費電力化の両立が可能であり、25Gbpsの高速伝送を従来の半分である1Gbpsあたり5mWで実現できることを確認しました(図4)。

図3 開発した技術にて高速化と低消費電力化を両立

図4 開発した光送受信回路のチップ写真と諸特性

効果

本技術により、消費電力を抑えながら、複数の光送受信回路を並べた毎秒テラビット級の高速伝送を実現する、サーバやスパコンの高性能化が期待されます。

今後

富士通研究所は、開発した技術をCPUや光モジュールのインターフェース部などに適用し、2018年度の実用化を目指します。さらに、次世代の高性能サーバやスパコンなどの製品への適用も検討していきます。

商標について

記載されている製品名などの固有名詞は、各社の商標または登録商標です。

以上

注釈

- 注1 富士通株式会社:

- 本社 東京都港区、執行役員社長 山本 正已。

- 注2 株式会社富士通研究所:

- 本社 神奈川県川崎市、代表取締役社長 佐相秀幸。

- 注3 Fujitsu Laboratories of America, Inc.:

- 米国Sunnyvale, CA、President & CEO 木村康則。

- 注4 技術研究組合 光電子融合基盤技術研究所(PETRA):

- 本部 東京都文京区、理事長 大槻次郎。

- 注5 独立行政法人 新エネルギー・産業技術総合開発機構(NEDO):

- 本部 神奈川県川崎市、理事長 古川一夫。

- 注6 1Gbps:

- 1秒間に1ギガビットのデータを伝送可能であること。

- 注7 シリコンフォトニクス技術:

- シリコン基板上に光素子を形成する技術。シリコンを用いることにより光回路を小型化でき、大規模集積が可能になる。また、光回路と電子回路を一体形成や製造コストの低減が可能になるなどの特長を持つ。

本件に関するお問い合わせ

株式会社富士通研究所

ICTシステム研究所 サーバテクノロジ研究部

![]() 044-754-2692(直通)

044-754-2692(直通)

![]() SiPh_ISSCC2015@ml.labs.fujitsu.com

SiPh_ISSCC2015@ml.labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。