PRESS RELEASE (技術)

2013年6月14日

株式会社富士通研究所

Fujitsu Laboratories of America, Inc.

CPU間の高速データ通信回路の低電力化を実現するクロック伝送技術を開発

送受信回路の消費電力を2割削減し、次世代サーバやスーパーコンピュータの高性能化に貢献

株式会社富士通研究所(注1)とFujitsu Laboratories of America, Inc. (注2)は、次世代サーバに搭載されるCPUなどのチップ間データ通信を行う送受信回路において、消費電力を2割削減可能なクロック伝送技術を開発しました。

近年、サーバのデータ処理能力向上のため、CPUの高性能化と共に、CPUなどのチップ間でのデータ通信速度の高速化が求められています。一方、高速化に伴い、通信を行う送受信回路に含まれるクロック伝送回路の消費電力が増大しています。今回、各送受信回路に小型の発振回路を搭載し、各発振器を同期させることで、従来のクロック伝送回路を不要とし、低電力化を実現したクロック伝送方式を開発しました。

本技術により、今後、次世代サーバやスーパーコンピュータなどの性能向上に貢献することが期待されます。

本技術の詳細は、6月11日(火曜日)から京都で開催される半導体回路技術に関する国際会議「2013 Symposium on VLSI Circuits」で発表します(発表番号19-2)。

開発の背景

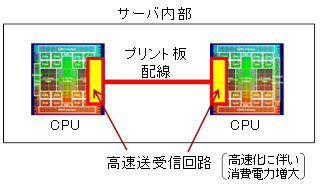

近年、クラウドコンピューティングを支えるデータセンターなどに向けて、サーバのデータ処理能力の向上が一層求められています。そのため、CPUの性能も向上し、さらに、CPUを多数接続した大規模システムも構築されており、CPUと周辺デバイス間でやり取りするデータ量はますます増大しています。これに対応するため、現在のサーバではCPU間などのデータ通信速度が毎秒数ギガビット(Gbps)から十数Gbpsと高速化が進んでいますが、高速化に伴い消費電力も増加しています。次世代の高性能サーバの実現に向けて、高速化と低電力化の両立への要求がますます強まっています。

図1 サーバ内部のCPU間などの高速データ通信

課題

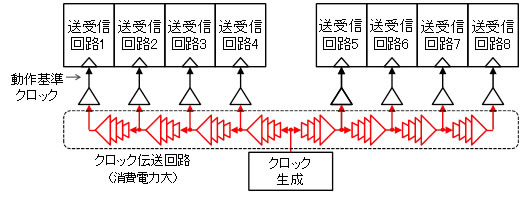

サーバを構成するCPUなどのチップ間データ通信の高速化に伴い、通信を行う送受信回路の消費電力が増大しており、特に、送受信回路全体の消費電力に占めるクロック伝送回路の消費電力の割合が大きくなっています。クロック伝送回路は、クロック生成回路で生成したクロック信号を減衰させずに各送受信回路まで伝送するために、比較的大きな振幅で、かつ、多段で構成される信号のため多くの電力を消費します。高速化と低電力化の両立のためには、低電力な新規クロック伝送回路を開発し、送受信回路の低電力化を進める必要があります。

図2 従来のクロック伝送方式

開発技術

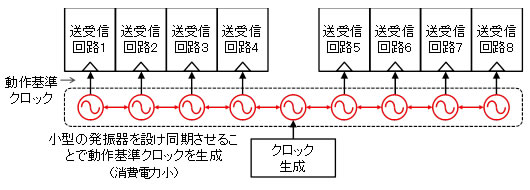

今回、各送受信回路に小型の発振回路を搭載し、各発振器を同期させることで、従来のクロック伝送回路を不要とし、低電力化を実現したクロック伝送方式(図3)を開発しました。

すべての動作基準クロック(発振器出力)は、クロック生成出力に同期するように制御されます。その結果、各送受信回路への動作基準クロックの周波数と位相は、クロック生成出力の周波数と位相と一致します。同期をとるための各発振器間の信号は、従来のクロック信号を伝送する場合に比べ小振幅な信号のため低電力化が可能です。

図3 新規クロック伝送方式

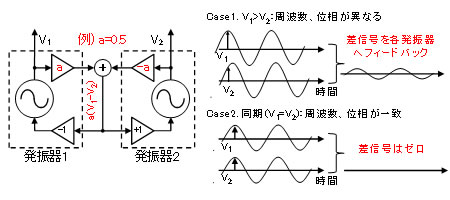

同期化を実現するにあたり、隣接した発振器出力の振幅差に比例した小振幅な信号を各発振器にフィードバックします(図4)。振幅差がゼロになるようフィードバックがかかるため、最終的には振幅差はゼロになり、各発振器の出力クロックの周波数と位相は一致します。すべての隣接した発振器が接続されており、かつ、その1つがクロック生成回路に接続されているため、すべての発振器はクロック生成出力に同期するよう動作します。このようにして、小振幅な差信号を生成、伝送することにより、複数の同期したクロックを生成することができます。

図4 小振幅信号により各発振器の同期化

本技術により、16ギガヘルツ(GHz)のクロック伝送回路の消費電力を75パーセント削減し、送受信回路全体の消費電力を2割削減することに成功しました。

効果

今回開発した技術を用いることで、次世代サーバやスーパーコンピュータなどの性能向上に大きく寄与することが期待されます。

今後

今回開発した技術を、サーバを構成するボード間のバックプレーンインターフェースなど、ビックデータを扱う製品分野への適用を進めていきます。

商標について

記載されている製品名などの固有名詞は、各社の商標または登録商標です。

以上

注釈

- 注1 株式会社富士通研究所:

- 代表取締役社長 富田達夫、本社 神奈川県川崎市。

- 注2 Fujitsu Laboratories of America, Inc.:

- President & CEO 木村康則、米国Sunnyvale, CA。

本件に関するお問い合わせ

株式会社富士通研究所

ICTシステム研究所

![]() 044-754-2690(直通)

044-754-2690(直通)

![]() hsio2013@ml.labs.fujitsu.com

hsio2013@ml.labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。