PRESS RELEASE (技術)

2013年2月1日

株式会社富士通研究所

携帯端末のベースバンド処理に対応した小型・高性能で

低電力なデジタル信号処理プロセッサを開発

スーパーコンピュータの技術を用い、スマートフォンなどの無線通信端末の低消費電力化に貢献

株式会社富士通研究所(注1)は、携帯電話のベースバンド処理に対応したデジタル信号処理プロセッサ(DSP:Digital Signal Processor)を開発しました。スーパーコンピュータでも用いられているベクトル処理アーキテクチャー(注2)を採用し、LTE(注3)などの無線処理の特徴である繰り返しの多い処理を効率よく実行することで、高い電力効率を実現しています。

28ナノメートル(nm)テクノロジーを用いたチップで、250メガヘルツ(MHz)動作時、12GOPS(1秒間に120億個)のデータ処理が可能です。また、メモリを除いたサイズが0.4平方ミリメートル(mm2)と小型であり、消費電力は30ミリワット(mW)と従来のDSPに比べ20%の低電力化を実現しました。

本DSPにより、携帯電話やスマートフォンの通話・利用時間、待ち受け時間の長期化が期待できます。また、信号処理のアルゴリズムの修正がDSPのプログラムの変更で可能となり、受信特性の微調整などを無線ベースバンドLSIの製造後にもできるようになり、開発期間の短縮にも貢献できます。

本技術の詳細は、4月22日(月曜日)から台湾で開催される国際会議「2013 VLSI-DAT(2013 International Symposium on VLSI Design, Automation and Test)」にて発表します。

開発の背景

近年、スマートフォンやタブレット端末に代表される無線通信端末が急速に普及しています。無線通信の高速化に伴い、従来の無線通信方式(GSMや3Gなど)に加えて、現在普及しつつあるLTEなどの新しい無線通信方式に対応した機種も登場しています。しかしこれらの各種無線通信方式に対応するためには、それぞれの方式に対応した信号処理(ベースバンド処理)回路が必要となるため、ベースバンド処理部の回路規模を小さく低電力で実現することが、端末の低コスト化や稼働時間を向上する上で特に重要になっています。

課題

一般的なベースバンド処理回路は、各無線通信方式に対応した専用のハードウェアで実現するため、方式の個数分の回路が必要になり、回路規模や実装面積を削減することが困難でした。また、DSPを用いてソフトウェアで各種無線通信方式に対応した機能を実現する方法も考えられますが、LTE方式では膨大な信号処理が必要となり、処理能力を向上しながら低電力化を実現するのが困難でした。

開発した技術

今回、携帯電話のベースバンド処理向けに、スーパーコンピュータでも用いられているベクトル処理アーキテクチャーを採用したDSPを開発しました。LTEなどの無線処理の特徴である繰り返しの多い処理を効率よく実行することで、高い電力効率を実現します。開発したDSPの特徴は以下の通りです。

- ベクトル処理アーキテクチャーを採用

DSPのアーキテクチャーにスーパーコンピュータでも用いられているベクトル方式を採用しました。一般的なプロセッサでは、1つの命令で1つのデータ(スカラーデータ)に対して処理を行いますが、ベクトル方式のプロセッサでは、1つの命令で複数のデータ(ベクトルデータ)に対してまとめて処理を行います。そのため、複数のデータに対して同じ処理を繰り返す場合、ベクトル方式では命令が1つで済むため、命令のメモリからの読み出し、解読などの処理が削減でき、その分の電力消費を低減できます。

LTEではOFDM(注4)と呼ばれる無線変調方式が採用されており、最大1200本のサブキャリアと呼ばれる情報が載せられた無線信号を束ねて通信します。DSPは受信した信号から情報を取り出すためには、サブキャリア1つずつに対して同じ処理を繰り返す必要があります。そのためベクトル方式が効果的になります。

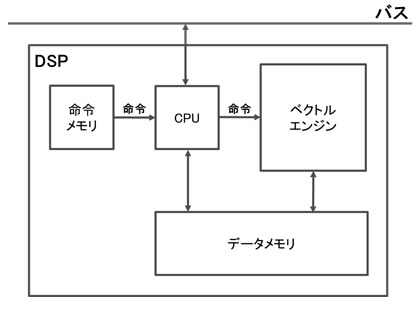

図1に開発したDSPのブロック構成を示します。DSPはベクトル方式のアーキテクチャーを採用したベクトルエンジンと、通常のCPUで構成されます。CPUが命令メモリからプログラムコードを読み込んで命令を解析し、その命令がベクトル方式に適した命令の場合はベクトルエンジンに転送され、実行されます。その他の命令の場合は、CPUがそのまま実行します。

図1 DSPのブロック構成図 - ベクトルエンジンをベースバンド処理向けに最適化

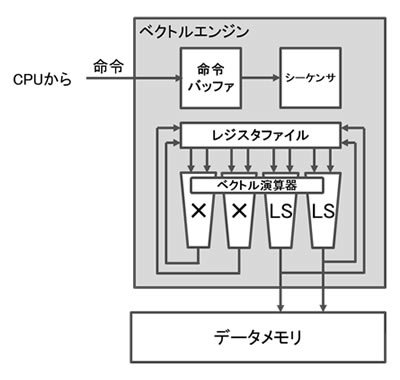

図2にベクトルエンジン部の内部構成を示します。CPUから転送された命令は命令バッファに格納されます。格納された命令はシーケンサが順次解読し、必要なベクトル演算器を制御して命令を実行します。1つの命令で処理できるベクトルデータの数(ベクトル長)を携帯電話のベースバンド処理向けに最適となるよう64個としました。また、64個のデータを1つずつ処理するのではなく、高速化のため演算器を8個並列に並べ一度に8個ずつ8回に分けて処理します。

ベクトルエンジンは回路規模を小さく、かつベースバンド処理向けに処理効率を高めるため、ベクトルデータ同士の乗算命令を処理する演算パイプライン(注5)2本と、メモリから一時的にデータを保持するレジスタファイルにベクトルデータをロードするロード命令(あるいは逆のストア命令)を処理可能な演算パイプライン2本の合計4本の構成としました。また4本すべてのパイプラインは、ベクトルデータ同士の加減算や論理演算も処理可能です。

図2 ベクトルエンジンのブロック構成図

効果

今回開発したベクトルエンジンを組み込むことにより、1つの命令で多くのデータを処理できるため、従来に比べ効率よくデータ処理が可能になり、無線ベースバンドLSIの低消費電力化に大きく貢献できます。28nmテクノロジーを用いたチップで、250MHz動作時、12GOPS(1秒間に約120億個)のデータ処理が可能です。また、メモリを除いたサイズが0.4mm2と小型であり、消費電力は30mWと従来のDSPに比べ20%の低電力化を実現しました。

本DSPにより、携帯電話やスマートフォンの通信・利用時間、待ち受け時間の長時間化に貢献できます。また、信号処理のアルゴリズムの修正がDSPのプログラムの変更で可能となり、受信特性の微調整などを無線ベースバンドLSIの製造後にもできるようになり、開発期間の短縮にも貢献できます。

今後

本DSPは、アクセスネットワークテクノロジ株式会社(注6)の通信処理プロセッサに搭載され、富士通製のスマートフォンなどに採用されています。今後、より通信速度の速い新しい無線通信規格にも対応できるよう、プロセッサの性能向上を進めていきます。

商標について

記載されている製品名などの固有名詞は、各社の商標または登録商標です。

以上

注釈

- 注1 株式会社富士通研究所:

- 代表取締役社長 富田達夫、本社 神奈川県川崎市。

- 注2 ベクトル処理アーキテクチャー:

- ベクトルデータ(配列データ)の演算を、1つの命令で処理するプロセッサ構成。

- 注3 LTE:

- Long Term Evolutionの略で、無線機器における最新の移動通信規格。

- 注4 OFDM:

- Orthogonal Frequency Division Multipleの略で、無線LANでも採用されている無線変調方式の1つ。

- 注5 演算パイプライン:

- 命令にしたがって演算処理を実行する回路。複数のステージに分割され、流れ作業的に処理を実行。

- 注6 アクセスネットワークテクノロジ株式会社:

- 代表取締役社長 坂田稔、本社 神奈川県川崎市。

本件に関するお問い合わせ

株式会社富士通研究所

プラットフォームテクノロジー研究所 プロセッサソリューション開発部

![]() 044-754-2783(直通)

044-754-2783(直通)

![]() psdl_vu@ml.labs.fujitsu.com

psdl_vu@ml.labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。