PRESS RELEASE (技術)

2011年2月2日

株式会社富士通研究所

世界初!銅を内部電極とした高速LSI用キャパシタのプロセス技術を開発

電流供給効率を従来の10倍へと向上させ、次世代の高速コンピュータの開発に寄与

開発の背景

近年、LSIの高速・高集積化が進み、多くの素子が同時に動作する際に、素子の周辺で一度に多くの電流が消費されるようになってきました。このとき、LSIの電源電圧は降下しやすく、正常な動作に影響を与えることがあります。多くの電流が消費される際には、即座に電流を補う必要があるため、LSIの近くにキャパシタを設置することが望まれています。

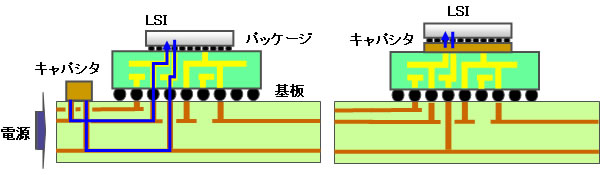

図1 従来の電源供給キャパシタ(左)と今回開発した電源供給キャパシタ(右)の実装形態 |

課題

従来は、電源供給キャパシタとしてセラミックチップコンデンサをLSIパッケージおよび基板の表面や裏面に搭載し、配線を介してLSIへ電流供給を行っていました(図1)。しかし、この方法では、キャパシタからLSIまでの接続配線が長いためにインピーダンスが大きく、将来の高速コンピュータではLSIの高速動作が不安定になる可能性があります。

また、キャパシタ部品の内部電極に抵抗値の比較的大きなニッケルなどを使用しているためにキャパシタ自身のインピーダンスも大きく、電源電流の高速供給に限界がありました。

開発した技術

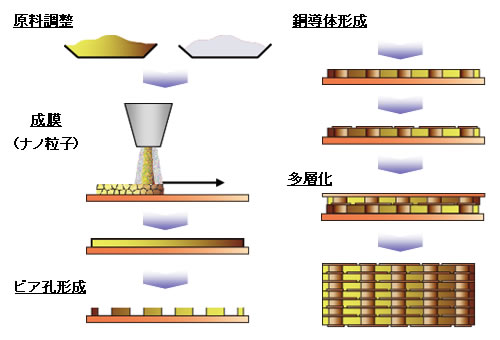

今回、高速LSIに電流を迅速に安定して供給するためのキャパシタの基本的なプロセス技術を開発しました(図2)。ナノ粒子成膜技術(注4)を用いて、以下のような特徴を持つキャパシタを作製することが可能になりました。

- 電気抵抗の低い銅の内部電極への適用(世界初)

- LSIの直下に接続が可能な微細な貫通電極構造

- 高容量化(1 μF/cm2・層)が可能で信頼性が高い薄膜の誘電体層

図2 開発した新しいキャパシタの製造フロー |

効果

銅を内部電極とすることで、キャパシタ自身のインピーダンスを低くすることが可能になり、キャパシタ・LSI間の配線長が短くなることから、電源供給ラインのインピーダンスを抑えることができます。

これにより、高速LSIの動作安定化に向けた電流供給効率が10倍以上向上し、コンピュータの高速化に寄与することが期待されます。

今後

今後は、キャパシタの端子の微細化と多層化技術の開発をさらに進め、2015年頃にコンピュータへの適用を目指します。

商標について

記載されている製品名などの固有名詞は、各社の商標または登録商標です。

以上

注釈

- 注1 株式会社富士通研究所:

- 代表取締役社長 富田達夫、本社 神奈川県川崎市。

- 注2 キャパシタ:

- 高速回路動作で生じる電源電圧の変動を抑えるために用いる電気を蓄える素子。

- 注3 インピーダンス:

- 交流回路における抵抗値(電圧と電流の比)。

- 注4 ナノ粒子成膜技術:

- ナノサイズのセラミック粒子を用いて無機材料の膜を形成する方法。

本件に関するお問い合わせ

株式会社富士通研究所

環境・エネルギー研究センター

電話: 046-250-8389(直通)

E-mail: asd-press@ml.labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。