PRESS RELEASE (技術)

2010年12月3日

株式会社富士通研究所

平面状の物質なら何にでも電源トランジスタを作製する技術を開発

基板を限定せず、銅やガラス、プラスチック上に電源回路の作製が可能に

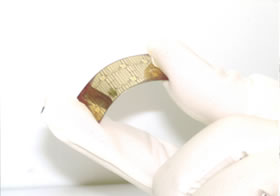

株式会社富士通研究所(注1)(以下、富士通研究所)は、銅やガラス、プラスチックなど、平面状の物質なら何にでも電源トランジスタの作製が可能な技術を開発しました。酸化亜鉛(ZnO)系の材料を用いて対象となる物質の上に高耐圧の電源トランジスタを作製し、トランジスタのチャネル部分をポリマー被膜で保護することによって、高耐圧での動作を実現しました。

本技術により、あらゆる平面状の物質への電源回路の作製が可能になります。また、センサーや圧電素子などへ応用することも可能です。

本技術の詳細は、米国時間11月29日(月曜日)から米国ボストンで開催される国際会議「2010 Material Research Society Fall Meeting」(2010 MRS Fall Meeting)にて発表いたしました。

開発の背景

環境負荷を低減するために、IT機器や家電、自動車などの電子機器における電源回路の電力削減が重要な課題となっています。さらに、汎用品である電源回路には、低コスト化も要求されており、電源回路用の低コストかつ高耐圧トランジスタの実現が期待されています。

酸化亜鉛(ZnO)は低損失の電源トランジスタを実現可能なワイドバンドギャップ半導体(注2)であり、どこにでもトランジスタを形成することが可能な材料です。最近ではガラス基板の上に形成する液晶テレビなどのディスプレイ向けトランジスタとして研究開発が行われています。

課題

酸化亜鉛(ZnO)を高耐圧の電源トランジスタとして作製するには、高耐圧を実現する上で必要となるチャネル材料の低濃度化が難しい点や、電界集中の原因となる材料表面に存在する電荷トラップ抑制という課題があります。これらの課題を解決して、電源用の高耐圧トランジスタを作製できる技術が必要とされていました。

開発した技術

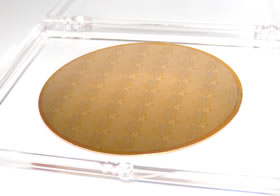

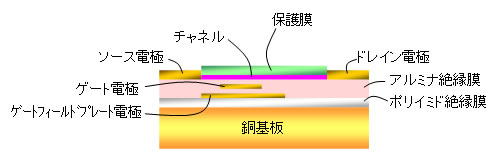

今回、材料としてインジウムガリウム酸化亜鉛(IGZO)を用い、電源トランジスタのチャネル部分をポリマー被膜で保護(図1)することによって、電源用の100V電圧でのトランジスタ動作に成功しました(図2)。さらに、高耐圧トランジスタをパッケージ材料である銅基板上に直接作製できるため、放熱性の確保が容易である上に、コストの低減も可能です。

|

|

効果

本技術により、あらゆる平面状の物質への電源回路の作製が可能になります。また、高電圧を発生するようなセンサーや圧電素子などへ応用することも可能です。

今後

今後、電源トランジスタとして要求される高耐圧化と、オン抵抗の低減を進め、2015年頃にIT機器への搭載を目指します。

商標について

記載されている製品名などの固有名詞は、各社の商標または登録商標です。

以上

注釈

- 注1 株式会社富士通研究所:

- 代表取締役社長 富田達夫、本社 神奈川県川崎市。

- 注2 ワイドギャップ半導体:

- ワイドバンドギャップを持つ半導体のこと。通常、トランジスタの耐圧は、バンドギャプが大きくなればなるほど高くなる。

本件に関するお問い合わせ

株式会社富士通研究所

環境・エネルギー研究センター エネルギー技術研究部

電話: 046-250-8234(直通)

E-mail: nano-mate@labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。