PRESS RELEASE (技術)

2009年11月27日

株式会社富士通研究所

世界初!大基板全面にグラフェントランジスタを低温で直接形成する技術を開発

低電圧・低消費電力の次世代トランジスタの実用化に大きく前進

株式会社富士通研究所(注1)は、次世代トランジスタの材料として期待されるナノメートルサイズの炭素材料(ナノカーボン)の1つであるグラフェン(注2)を、一般的な半導体製造プロセスである化学気相成長法(以下、CVD法)(注3)を用いて絶縁基板上に低温で直接形成する技術を開発し、大基板の全面にトランジスタを形成することに世界で初めて成功しました。さらに、従来のグラフェンの形成温度が800~1,000℃であるのに比べ、形成温度を650℃と大幅に引き下げたことにより、さまざまな絶縁基板上に直接グラフェントランジスタを形成することが可能となります。

グラフェンは高い電子・ホール移動度を持ち、低電圧・低消費電力で動作する次世代トランジスタの材料として期待されています。本技術の開発により、グラフェントランジスタの実用化に向けて大きく前進しました。

本技術の詳細は、11月30日(月曜日)から米国・ボストンで開催される国際会議「Materials Research Society 2009 Fall Meeting」(MRS 2009 Fall Meeting)で発表いたします。

背景

現在LSIに使われるトランジスタのチャネル材料(電気の通り道)にはシリコンが使われており、デバイスサイズを小さくする微細化によって高速化や低消費電力化が実現されてきました。しかし、近年は微細化の限界に近づきつつあると言われており、性能向上が次第に困難になってきています。そのため、ゲルマニウム、ガリウム砒素のほか、グラフェンをチャネル材料とした次世代のトランジスタ開発が盛んに行われています。

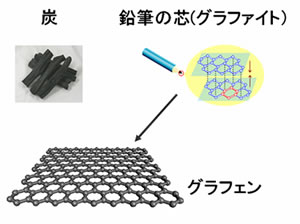

グラフェンは、鉛筆の芯などの材料としても使われている層状物質グラファイトの一層分のことで、炭素原子が六角形の網の目のように並んだシート状の構造を持ちます(図1)。グラフェンは、極めて優れた電気特性を持つことが明らかになっています。半導体で一般的に使用されているシリコンと比較して、非常に高い電子移動度を持つことが実験的に示されており、高速、あるいは低電圧で動作するトランジスタを実現できると考えられています。

|

従来の課題

グラフェンを利用したトランジスタの試作は数年前から行われています。グラフェンを基板上に配置するために、主に以下の方法が利用されてきました。

- 剥離・転写法

グラファイト結晶からテープで剥がして基板に貼り付ける方法。

- CVD・転写法

800~1,000℃程度の温度で、CVD法により金属触媒膜上にグラフェンを形成し、それをほかの基板上に移しかえる方法。

- SiC(注4)表面熱分解法

半導体であるSiC基板を1,200℃程度以上の高温で熱処理し、SiC基板表面にグラフェンを形成する方法。

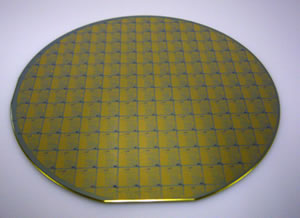

金属触媒を利用するCVD法は、任意の基板上にグラフェンを形成できる有力な方法です。しかし、導体である金属上ではトランジスタの形成ができないため、従来は別の基板に形成したグラフェンを絶縁基板に転写することによってトランジスタの形成が行われてきました。この方法では薄い膜であるグラフェンにシワがよりやすく、現在主流となっている直径300mmのウエハーのような大基板への適用が容易ではありません。実用化のためには基板サイズに関わらず一様にトランジスタを形成できる技術が課題となっていました。

また、通常は800℃以上の温度でグラフェンを形成するため、利用できる基板の種類が限られてしまうという課題もありました。

新技術の概要

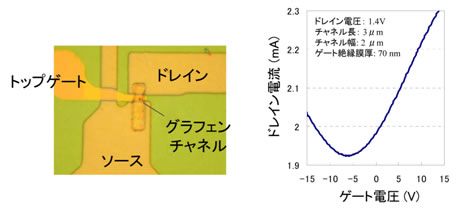

富士通研究所は、世界で初めて、650℃と低い温度で絶縁基板上にグラフェンをCVD形成し、グラフェントランジスタを基板全面に直接形成する技術を開発しました。利用した基板は直径75mmの酸化膜付シリコン基板ですが、さらに大きな300mmサイズの大きな基板にも適用可能です(図2)。

開発した技術のポイントは以下の通りです。

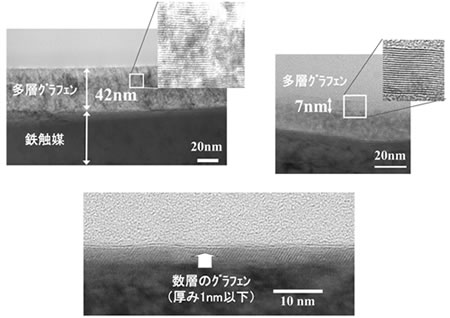

- CVD法により厚みを制御した多層グラフェンを低温で基板全面に合成

触媒である鉄膜を酸化膜付きシリコン基板上に堆積し、アセチレンを原料とした熱CVD法により、その鉄膜上に厚みを制御してグラフェンを形成する技術を開発しました。図3に示すように、厚み1nm程度の数層のグラフェンから50nm程度の多層グラフェンまで、さまざまな厚みのものを形成することが可能です。また、富士通研究所独自のCVD技術により、従来800~1,000℃程度だった合成温度を650℃程度と低い温度で実現し、シリコン基板のみならず、熱に弱いガラスなどのさまざまな基板上に直接グラフェンを形成する可能性がひらけました。

図2 グラフェントランジスタを形成した直径75mmの酸化膜付Si基板

図3 さまざまな厚みに合成されたグラフェン - 転写を用いないグラフェントランジスタの形成プロセスを開発

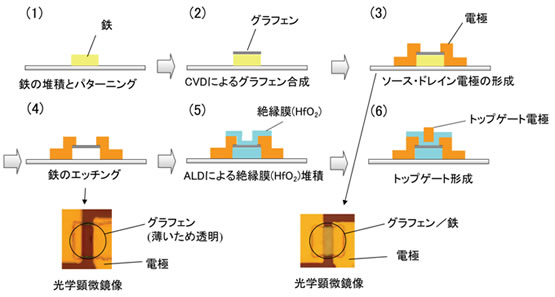

グラフェンをチャネル材料として使用したトランジスタの形成プロセスを開発しました(図4)。本プロセスは基板サイズを選ばないため、大基板にも適用可能です。

- まず、通常のフォトリソグラフィープロセス(注5)を用い、鉄膜をあらかじめチャネル形状に加工しておきます。

- 次に、CVD法により鉄膜上にグラフェンを形成します。

- その後、ソース・ドレイン電極(チタン・金積層膜)をグラフェンの両端に形成しグラフェンを「固定」します。

- この状態で、酸で鉄膜のみを除去すると、浮いた状態のグラフェンがソース・ドレイン電極の間を架橋したような構造となります。

- 続いて、薄膜形成法の1つである原子層堆積法(ALD)(注6)により、グラフェンを覆うように酸化ハフニウム(HfO2)膜を堆積し、グラフェンを安定化します。

- 最後にグラフェン上にHfO2を介してゲート電極を形成することにより、グラフェントランジスタを形成します。

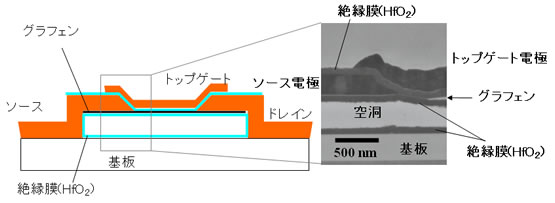

グラフェントランジスタの性能向上のためには、4.のような浮いた状態のグラフェンを形成し、グラフェンの両面をクリーニングできることが重要です。また今回適用したALD法では、浮いた状態のグラフェンを覆うように絶縁膜の堆積を行うことができます(図5)。

図4 グラフェントランジスタ形成プロセス

図5 浮いたグラフェンを利用したトランジスタの模式図と断面写真

効果

今回開発した技術により、大基板の全面にグラフェントランジスタを形成することが可能になりました。形成したトップゲート・トランジスタのドレイン電流のゲート電圧依存性の一例を、図6に示します。グラフェンに特徴的な両極特性(注7)が得られました。

|

グラフェンは厚さが数ナノメートル程度以下の場合に光を良く通すため、ディスプレイなどに用いられる薄膜トランジスタのチャネル材料や電極材料としても期待されます。

本技術でのグラフェン合成温度は650℃程度であり、良く使用されている一般的なガラス上に直接合成可能な温度(550℃程度)に近いものです。近い将来、大きなガラス基板上に直接グラフェントランジスタを形成することも夢ではありません。

今後

今回の開発により、グラフェントランジスタを利用した電子デバイスの実現に大きく前進しました。しかし、実際の電子デバイスへの応用のためには解決しなければならない課題が数多くあります。今後はそれらの課題を解決していくことで、グラフェンの特徴を活かした低電圧で駆動可能なトランジスタを開発していきます。これによって、従来の10分の1から100分の1という低消費電力LSIや、それを利用したIT機器を実現し、省エネルギー化に寄与していきます。

商標について

記載されている製品名などの固有名詞は、各社の商標または登録商標です。

以上

注釈

- 注1 株式会社富士通研究所:

- 代表取締役社長 村野和雄、本社 神奈川県川崎市。

- 注2 グラフェン:

- 炭素原子が六角形の網の目状に並んだ構造で、グラファイトはこのグラフェンが積層したもの。

- 注3 化学気相成長法:

- Chemical Vapor Deposition。反応容器内で原料ガスを熱などにより分解して基板上に薄膜や構造体を合成する方法。半導体デバイスの製造プロセスで一般的に使用されている。

- 注4 SiC:

- Silicon Carbide、炭化ケイ素。

- 注5 フォトリソグラフィープロセス:

- 感光性の材料を基板上に塗布し、パターンが形成されたマスクを通して紫外線などを基板に照射することにより、露光のされている部分、されていない部分のパターンを基板上に形成する方法。半導体デバイスの製造プロセスに不可欠。

- 注6 原子層堆積法(ALD):

- Atomic Layer Deposition。2種類以上の原料ガスを交互に反応容器内に導入することにより、物質を1原子層ずつ制御性良く堆積する方法。極めて薄い絶縁膜の堆積などに使用される。

- 注7 両極特性:

- p型トランジスタ、n型トランジスタの両方の特性を併せ持つこと。

技術に関するお問い合わせ

株式会社富士通研究所

ナノエレクトロニクス研究センター

電話: 046-250-8234(直通)

E-mail: nano-mate@labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。