PRESS RELEASE (技術)

2008年12月17日

株式会社富士通研究所

富士通マイクロエレクトロニクス株式会社

CMOSロジックプロセスを用いたパワーアンプ向け高耐圧トランジスタを開発

~パワーアンプとCMOSロジック制御回路の1チップ化を可能に~

株式会社富士通研究所(注1)と富士通マイクロエレクトロニクス株式会社(注2)は、CMOSロジック(注3)プロセスを用いて、ワイヤレス機器向けパワーアンプに適した高耐圧トランジスタを開発しました。今回、世界で初めて、45ナノメートル(以下、nm)世代のCMOSプロセスを用いて、トランジスタの耐圧を10ボルト(以下、V)まで向上させることに成功し、WiMAX(注4)のような高周波向けのパワーアンプに適用可能な高出力特性を有するトランジスタを開発しました。この技術により、パワーアンプとCMOSロジック制御回路を1チップに集積することが可能となり、高性能で低コストなパワーアンプを提供することが可能となります。

なお、本技術の詳細は、米国 サンフランシスコで12月15日から開催されている半導体の国際学会、「2008 IEEE International Electron Devices Meeting (IEDM)」にて発表しました。(講演番号19.1)

背景

ワイヤレス機器向けパワーアンプは、高周波領域で高出力電力が要求されるため、現在は、ガリウム砒素(GaAs)などの化合物半導体が使われており、汎用的なCMOSロジック半導体を用いた制御回路とは別のチップとして実装されています。これらを1チップに集積することができればモジュールの低コスト化に結びつき、WiMAXやLTE(注5)などに対応するワイヤレス機器を広く普及させることができると考えられています。このためCMOSロジック技術と親和性が高く、WiMAXなどで要求されるパワーアンプの出力性能を満たすことができるトランジスタの開発が必要になります。

課題

WiMAXなどの高周波向けパワーアンプに要求される出力電力を実現するためには、通常のCMOSロジックプロセスを用いたトランジスタでは耐圧が十分ではありません。このため、CMOSロジックプロセスとの親和性を保ちながら、トランジスタの破壊につながるドレイン付近の電界を緩和させた構造を実現し、トランジスタの高耐圧化を図る必要があります。また、一般的に高耐圧構造は、トランジスタのオン抵抗(注6)を上昇させてしまい、高周波領域で十分な性能を得ることが困難になるため、耐圧を向上させながら、オン抵抗の上昇を抑制することが課題となります。

技術の概要

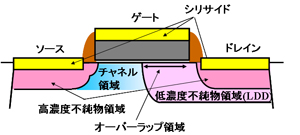

上記の課題を解決するために、次のような特長を持つ新構造のトランジスタを開発しました。(図1)

図1 開発したトランジスタの構造 |

- トランジスタのドレイン側に不純物を低濃度で注入した領域(以下、LDD: Lightly Doped Drain)を形成し、その領域をゲートとオーバーラップさせます。これによりドレインに加わる横方向の電界とゲート酸化膜に加わる電界が緩やかになるため、耐圧を高めることができます。

- トランジスタのチャネルの不純物分布を、横方向に勾配をもたせます。これによりドレイン側のチャネルの不純物濃度が低くなるため、オン抵抗の主要因であるドレインの抵抗が上昇することを抑制し、同時に、ドレインに加わる横方向の電界が低減できることから耐圧も向上します。

従来、CMOSトランジスタで耐圧を向上させるには、ゲートとドレインの間隔を広げるという方法が採られていましたが、その方法に比べても、上記の構造によりゲートとドレインの間隔を広げる必要がないためオン抵抗の上昇を抑えることができます。

また、この構造のトランジスタは、通常の3.3VのI/Oトランジスタ(注7)の製造工程に、LDD領域を形成する工程と専用のチャネル領域を形成する工程を追加するのみで製造でき、既存のプロセスに対して親和性が高いと考えられます。

効果

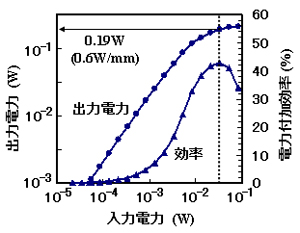

図2 パワートランジスタの特性 (測定周波数 2.1GHz, ゲート幅0.32mm) |

今回、45nm世代の製造技術で、通常の3.3Vの I/Oトランジスタに本技術を適用したところ、世界で初めて、耐圧を6Vから10Vに向上させることができました。パワーアンプ向けトランジスタの特性としては、最大発振周波数が43ギガヘルツ(以下、GHz)で、ゲート幅1 mmあたり0.6ワット(以下、W/mm)の最大電力を達成(図2)し、今回開発したトランジスタが、WiMAX向けパワートランジスタとして十分な性能を有していることを確認しました。また基本的な信頼性評価を行い、良好な結果を得ています。

今後

上記の技術開発により、先端的なCMOSロジック技術にパワーアンプ向け高耐圧トランジスタを搭載する目処をつけることができました。今後、この技術をさらに発展させ、パワーアンプと制御回路の1チップ化を図り、低コストで高性能なパワーアンプモジュールの提供を実現していきます。

以上

注釈

- 注1 株式会社富士通研究所:

- 代表取締役社長 村野和雄、本社 神奈川県川崎市。

- 注2 富士通マイクロエレクトロニクス株式会社:

- 代表取締役社長 岡田晴基、本社 東京都新宿区。

- 注3 CMOSロジック:

- N型とP型のMOS(Metal Oxide Semiconductor)トランジスタを相補的に接続して構成されている論理回路。消費電力が小さく、現在の集積回路の主流となっている。

- 注4 WiMAX:

- Worldwide Interoperability for Microwave Accessの略。無線通信技術の規格の1つであり、今後のワイヤレス機器に広く普及することが期待されている。

- 注5 LTE:

- Long Term Evolutionの略。新しい携帯電話の通信規格。2010年頃からのサービス開始が見込まれている。

- 注6 オン抵抗:

- トランジスタがオン状態の時の、ドレイン電極・ソース電極間の抵抗。オン抵抗が小さいほど、高効率・高出力の電力特性を得ることができる。

- 注7 I/Oトランジスタ:

- 外部との信号のやりとりを行うために集積回路に組み込まれている入出力回路用のトランジスタ。入出力回路部では、集積回路内部に比べ高い電源電圧を用いる場合が多く、3.3V用のI/Oトランジスタが広く利用されている。

関連リンク

本件に関するお問い合わせ

富士通マイクロエレクトロニクス株式会社

共通技術本部 共通テクノロジ開発統括部

電話: 042-532-1488 (直通)

E-mail: cmos-pa@ml.labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。