PRESS RELEASE (技術)

2008年6月17日

株式会社富士通研究所

富士通マイクロエレクトロニクス株式会社

32nm世代向けに低消費電力化CMOS技術を開発

~製造工程数の増加を抑制~

なお、本技術の詳細は、米国ホノルルで6月17日(火曜日)から開催される半導体の国際会議「2008 Symposium on VLSI Technology」にて発表します。

背景

ロジックLSIの基本素子であるNMOSトランジスタ(以下、NMOS)およびPMOSトランジスタ(以下、PMOS)の低消費電力化には、電源電圧の低減が有効です。一方、単に電源電圧を下げるだけではMOSトランジスタが流すことができるオン電流が減少し、動作速度の低下を招きます。この課題に対し、2010年ごろから実用化が予想されている32nm世代ロジックLSIでは、高速化あるいは低消費電力化に向けて、各社がゲート電極材料として従来の多結晶シリコンではなくメタル材料を採用する見込みです。メタルゲート電極はMOSトランジスタが供給することができるオン電流を大幅に増加させることができるため、動作速度を劣化させることなくロジックLSIを低消費電力化することが可能です。

課題

32nm世代のロジックLSIにおけるメタルゲート電極では、低い電圧でも従来と変わらないオン電流を実現するために、NMOSとPMOSそれぞれに異なるメタル材料のゲート電極が必要となり、新材料の導入と製造工程数の増加によるコスト増の問題があります。

技術の概要

今回、NMOSとPMOSそれぞれに新技術を開発することで、新材料の導入と製造工程数の増加によるコスト増を最小限に抑えながら、これまでに報告されている32nm世代向けメタルゲート技術と同様に、動作速度を落とさずに低消費電力化を実現しました。

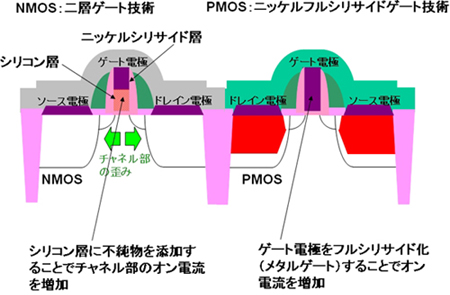

- NMOSの二層ゲート技術

NMOSは、従来のニッケルシリサイド(注3)層とシリコン層からなる二層のゲート電極構造のままとし、シリコン層に不純物を添加することで、オン電流が流れるチャネル部に大きな歪みを加え、オン電流を増加させることに成功しました。この結果、動作速度を劣化させることなく、より少ない消費電力での動作を可能にします。

- PMOSのニッケル(Ni)フルシリサイドゲート技術

高温熱処理と構造の最適化により、PMOSのゲート電極だけを、従来からシリサイドの材料として広く使われているニッケルでフルシリサイド化(注4)にすることに成功しました。ニッケルシリサイドによるゲート電極はメタルゲート電極として機能するため、特にPMOSの多結晶シリコンで起こるゲート電極の空乏化(注5)による著しい性能低下が無くなり、オン電流を増加させることができました。この結果、PMOSのニッケルフルシリサイドゲート技術により、45nm世代ロジックLSIと比べて動作速度を劣化させることなく、少ない消費電力での動作を可能にします。

|

効果

本技術導入による製造工程数の増加は、これまでに報告されている32nm世代向けメタルゲート技術と比べて、6工程から1工程へと、大幅に抑制できます。この結果、32nm世代向けメタルゲート技術と比べ、新技術導入によるコスト増大は1%以下で済みます。

性能面では、32nm世代向けメタルゲート技術と同様、45nm世代ロジックLSIに比べて動作速度を落とさずに電源電圧を下げることができ、動作時の消費電力を約40%削減します。

今後

今後もさらなる技術開発を行い、低消費電力32nm世代テクノロジーの実現を目指します。

以上

注釈

- 注1 株式会社富士通研究所:

- 代表取締役社長 村野和雄、本社 神奈川県川崎市。

- 注2 富士通マイクロエレクトロニクス株式会社:

- 代表取締役社長 岡田晴基、本社 東京都新宿区。

- 注3 ニッケルシリサイド:

- シリサイドはシリコンと高融点金属との化合物。ニッケルのほか、コバルトやチタンを使ったものがある。

- 注4 フルシリサイド化:

- 通常、ゲート電極の上部のみをシリサイド化し、ゲート酸化膜に接する下部にはシリコンを残している。フルシリサイド化はゲート電極全てをシリサイド化すること。

- 注5 空乏化:

- ゲート電圧を印加した時に、ゲート電極内のゲート酸化膜と接する部分で自由キャリア数が減ること。電気的にはゲート酸化膜厚が厚くなることと等価のため、オン電流が減少する。

関連リンク

本件に関するお問い合わせ

株式会社富士通研究所

シリコンテクノロジ開発研究所

電話: 0594-24-2294 (直通)

E-mail: silicon-ask@ml.labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。