PRESS RELEASE (技術)

2007-0247

2007年12月12日

株式会社富士通研究所

富士通株式会社

32nm世代以降のロジックLSI向け高信頼性多層配線技術を開発

~32nm世代に必要な配線の低抵抗化と信頼性の確保の両立に成功~

なお、今回の技術については、米国ワシントンD.C.で12月10日から開催されている半導体の国際学会、IEDM(International Electron Devices Meeting)にて発表しました。(講演番号19.6)

背景

マイクロプロセッサの高性能化や携帯情報端末の多機能化、小型化などにともない、ロジックLSIには、高性能化、高集積化、省電力化が要求され、LSIに用いる多層配線においても、微細化が推し進めらています。例えば、現在開発段階にある32nm世代ロジックLSIでは幅50nmの銅(Cu)配線が予定されています。LSIの高性能化のためには、このような微細な配線において、配線抵抗の上昇を抑えるとともに、配線の劣化を抑制し高い信頼性を確保する技術が重要となってきます。

課題

45nm世代までのLSIで用いられるCu配線は、Cuを保護するためにバリアメタルで周りが覆われています。バリアメタルは絶縁膜中へのCuの拡散や絶縁膜からCuへの酸素の侵入を抑制するために必要なもので、バリアメタルを厚くすれば信頼性を確保することができます。しかし32nm世代のような微細なCu配線に対してバリアメタルの占める割合が大きくなると、配線抵抗が増加してしまうため、配線抵抗の低減と信頼性の確保をいかに両立させるかが課題となっています。

技術の概要

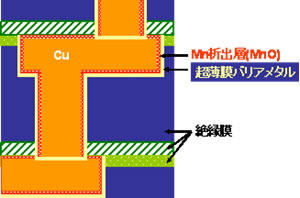

今回、超薄膜のバリアメタル上にマンガン(Mn)を添加したCu配線を形成することで、配線抵抗の低減と高信頼性の確保を両立させることに成功しました。この配線構造(図1)は以下のような工程により作製されます。

図1 開発した多層配線構造 |

- 絶縁膜へCuが拡散するのを防止する超薄膜のバリアメタルを成膜します。

- Mnを含むCuシード層を成膜した上、配線材料のCuをめっきします。

- その後の工程で350℃を超える温度が加わり、Cu配線の周囲を取り囲むようにバリアメタルよりさらに薄いMn析出層が形成されます。

このMn析出層がバリアメタルの酸化を抑制するため、超薄膜のバリアメタルで、従来のバリア性能を維持することが可能になりました。

効果

本方式を用いた多層配線技術により、従来の45nm世代まで用いられていた、Cu配線とバリアメタルを組み合わせた方法に対して、バリアメタルを3分の1に薄膜化し、配線抵抗を効果的に低減し、国際半導体ロードマップ(ITRS(注3))において提示されている、32nm世代の標準的な配線抵抗値を満たすことが可能になります。またLSIの配線における経年劣化の要因となるエレクトロマイグレーションに対する耐性寿命は従来の47倍に向上し、32nm世代の高集積で微細な配線に適用できるだけの高い信頼性を確保することができます。

今後

上記の技術開発により、32nm世代以降のロジックLSIに適用する多層配線技術に目処をつけることができました。今後、この技術をさらに発展させ、高性能、高集積、低省電力なLSIを提供していきます。

以上

注釈

- 注1 株式会社富士通研究所:

- 代表取締役社長 村野和雄、本社 神奈川県川崎市。

- 注2 エレクトロマイグレーション:

- 高い密度で電流が流れる時、配線中の銅原子が徐々に移動して空孔が発生・成長し、配線抵抗が増大する現象。ひどい場合は断線に至る。32nm世代以降では電流密度の上昇にともなってこの現象が顕著になるため、その耐性の向上が大きな課題。

- 注3 ITRS:

- International Technology Roadmap for Semiconductorの略。日本、米国、欧州、韓国、台湾の委員で毎年作成している半導体の各種ロードマップ。

関連リンク

本件に関するお問い合わせ

株式会社富士通研究所

シリコンテクノロジ開発研究所

電話: 042-532-1253 (直通)

E-mail: silicon-ask@ml.labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。