PRESS RELEASE (技術)

2007-0136

2007年6月18日

株式会社富士通研究所

富士通株式会社

45nm世代ロジックLSI向け低消費電力・高性能化技術を開発

~新たな熱処理技術と多層配線技術を導入~

株式会社富士通研究所(注1)と富士通株式会社(以下、富士通)は、低消費電力、高速トランジスタ技術と高性能配線技術を組み合わせた45ナノメートル(以下、nm)世代ロジックLSI向けプラットフォーム技術を開発しました。従来の45nm世代技術と比べて、待機時に無駄に流れてしまう洩れ電流を5分の1に低減し、配線遅延時間を約14パーセント(%)短縮しました。この45nm世代プラットフォーム技術の実現によって、より高速、小型で低消費電力のLSIをお客様に提供できるようになります。

なお、今回の技術の詳細は、6月12日から14日まで京都で開催された半導体の国際学会、Symposium on VLSI Technologyにて発表しました(講演番号10A-1および7B-4)。

背景

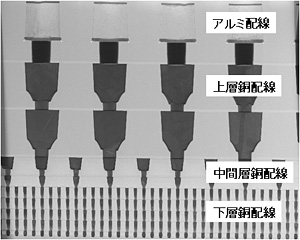

図1 開発した下層フルNCS構造の 45ナノメートル多層配線 |

ロジックLSIでは、各種機器の多機能化に対応した高機能化や、マイクロプロセッサのマルチコア化対応など、これまで以上に高集積化の重要性が高くなりつつあります。このような動向を踏まえ、45nm世代向けロジックテクノロジーは、集積度増大と速度性能向上に伴う消費電力の増大を抑制させる技術がますます重要となってきています。

LSIの集積度を上げるには、世代とともにトランジスタのゲート長の短縮や、配線間隔の微細化が必要になります。また、高速化には、LSI内に集積された何億個ものトランジスタを繋ぐ配線(図1)の遅延時間を短くすることが必要です。

課題

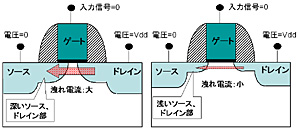

トランジスタのゲート長が短くなると、ゲートに信号電圧が加わっていない時(携帯電話の待ち受け状態など、演算処理などの作業がなくスタンバイの状態)にソースとドレインの間に流れる洩れ電流が増大し、消費電力が増大することが課題となっています。

また、配線幅と配線間隔は45nm世代では共に最小で65nmになります。微細化による配線抵抗の増大に加えて、層間絶縁膜の誘電率が前世代と同じでは配線容量が増加し、配線遅延時間の増大につながるため、より誘電率の低い材料が必要になります。

技術の概要

- 新熱処理技術

洩れ電流を低減するにはソースおよびドレイン部を浅く形成することが有効です(図2)。しかし、単純に浅くすると、ソースおよびドレイン部の抵抗が増大し、トランジスタ性能は劣化します。そこで今回、新たな熱処理技術(ミリ秒熱処理、Millisecond Annealing, MSA)を開発しました。本技術は、従来の熱処理方法と比べて高温のため抵抗の低減が可能で、かつ短時間の熱処理であるため浅いソースおよびドレイン部を形成可能で洩れ電流を低減できます。

- 高性能多層配線技術

これまでに報告されている層間絶縁膜の中で誘電率(k)が最も低い材料(k=2.25)のNano Clustering Silica (NCS)を、最小の配線間隔が適用される下層配線領域に導入しました。

NCSは、膜中に微小な空孔を持った絶縁物で、低誘電率と高い機械的強度を両立した材料です。富士通は65nm世代から部分的にNCSを導入しましたが、45nm世代ではNCSを同一配線層間だけでなく異種配線層間にも適用し、さらなる配線容量の低減を実現しました。

効果

新熱処理技術により、トランジスタの抵抗の増大を抑制しつつ、洩れ電流を従来の5分の1に低減しました。これにより、たとえば携帯電話の待ち受け時間を最大で5倍に延ばすことが可能になります。

また、高性能多層配線技術により、配線遅延を国際半導体ロードマップ(ITRS(注2))の標準的な45nm世代の配線技術と比較して約14%短縮しました。

今後

図2 ソース、ドレイン部の深さと洩れ電流 |

| 拡大イメージ |

上記の二つの技術開発の結果、システムのスタンバイ時の電力低減と動作時の高速化の両立が可能となります。富士通は今後2008年を目処にユビキタス社会での携帯機器への適用に最適なLSIを提供していきます。

以上

注釈

- 注1 株式会社富士通研究所:

- 代表取締役社長 村野和雄、本社 神奈川県川崎市。

- 注2 ITRS:

- International Technology Roadmap for Semiconductorの略。日本、米国、欧州、韓国、台湾の委員で毎年作成している半導体の各種ロードマップ。

本件に関するお問い合わせ

株式会社富士通研究所

シリコンテクノロジ開発研究所

電話:042-532-1253 (直通)

E-mail:silicon-ask@ml.labs.fujitsu.com

プレスリリースに記載された製品の価格、仕様、サービス内容、お問い合わせ先などは、発表日現在のものです。その後予告なしに変更されることがあります。あらかじめご了承ください。